# DESIGN AND IMPLEMNTATION OF AN EDUCATIONAL AM RECEIVER WITH FPGA USING SDR TECHNIQUES

Ali Ibrahim Khalifa HANDER

# 2021 MASTER THESIS ELECTRICAL AND ELECTRONICS ENGINEERING

Thesis Advisor Assist. Prof. Dr. Bilgehan ERKAL

# DESIGN AND IMPLEMNTATION OF AN EDUCATIONAL AM RECEIVER WITH FPGA USING SDR TECHNIQUES

Ali Ibrahim Khalifa HANDER

T.C. Karabuk University Institute of Graduate Programs Department of Electrical and Electronic Engineering Prepared as Master Thesis

Thesis Advisor Assist. Prof. Dr. Bilgehan ERKAL

> KARABUK January 2021

I certify that in my opinion the thesis submitted by Ali Ibrahim Khalifa HANDER titled "DESIGN AND IMPLEMNTATION OF AN EDUCATIONAL AM RECEIVER WITH FPGA USING SDR TECHNIQUES" is fully adequate in scope and in quality as a thesis for the degree of Master of Science.

Assist. Prof. Dr. Bilgehan ERKAL ...... Thesis Advisor, Department of Electrical and Electronic Engineering

This thesis is accepted by the examining committee with a unanimous vote in the Department of Electrical and Electronic Engineering as a master thesis. January 19, 2021

| Examining Committee Members (Institutions)       | <u>Signature</u> |

|--------------------------------------------------|------------------|

| Chairman: Assoc. Prof. Dr. Salih GÖRGÜNOĞLU (KU) |                  |

| Member : Assoc. Prof. Dr. Hüseyin DEMIREL (KBU)  |                  |

| Member : Assist. Prof. Dr. Bilgehan ERKAL (KBU)  |                  |

The degree of Master of Science by the thesis submitted is approved by the Administrative Board of the Institute of Graduate Programs, Karabuk University.

Prof. Dr. Hasan SOLMAZ ...... Director of the Institute of Graduate Programs

"I declare that all the information within this thesis has been gathered and presented in accordance with academic regulations and ethical principles and I have according to the requirements of these regulations and principles cited all those which do not originate in this work as well."

Ali Ibrahim Khalifa HANDER

# ABSTRACT

#### M. Sc. Thesis

# DESIGN AND IMPLEMNTATION OF AN EDUCATIONAL AM RECEIVER WITH FPGA USING SDR TECHNIQUES

Ali Ibrahim Khalifa HANDER

Karabük University Institute of Graduate Programs Department of Electrical and Electronic Engineering

> Thesis Advisor: Assist. Prof. Dr. Bilgehan ERKAL January 2021, 102 pages

In this study, an AM receiver is designed and implemented in FPGA using SDR techniques. The main purpose of the study is to provide a cheap and simple FPGA based platform for education of SDR basics. Firstly in the study, a simulation environment is set using MATLAB scripts. A set of test signals are recorded and used to generate an AM test signal using MATLAB scripts. The signal is used in simulation and test of FPGA implementation. Simulation code is also used as a framework in the VHDL design of the FPGA based SDR system. Another MATLAB script is written to analyze the test and simulation results and make a comparison. Where the results obtained from those tests on the two signals, it proved that the tests with the signal A1 are better than the tests with the signal A2, as the higher SNR ratio means the better. When comparing the actual real-world values with the simulations for each test signal, it is noted that the real-world SNR results are slightly lower than the simulations SNR. Where test results provided a SNR higher than

20dB, which is an acceptable level for an AM receiver. Where, test and simulation results prove FPGA AM RX system a useful candidate for AM demodulation and reception. The designed and implemented FPGA AM RX system is also a good utility in the education of basic SDR principles which is the main focus of this study.

**Key Words** : SDR, FPGA, VHDL, SNR, MATLAB, RX, AM. **Science Code :** 90523

# ÖZET

## Yüksek Lisans Tezi

# SDR TEKNİKLERİNİ KULLANARAK FPGA İLE EĞİTİM AMAÇLI BİR ALICININ TASARIMI VE UYGULANMASI

Ali Ibrahim Khalifa HANDER

Karabük Üniversitesi Lisansüstü Eğitim Enstitüsü Elektrik-Elektronik Mühendisliği Anabilim Dalı

> Tez Danışmanı: Dr. Öğr. Üyesi Bilgehan ERKAL Ocak 2021, 102 sayfa

Bu çalışmada, bir AM alıcısı, SDR teknikleri kullanılarak FPGA'da tasarlanmış ve uygulanmıştır. Çalışmanın temel amacı, SDR temellerinin eğitimi için ucuz ve basit bir FPGA tabanlı platform sağlamaktır. İlk olarak çalışmada MATLAB betikleri kullanılarak bir simülasyon ortamı oluşturulmuştur. MATLAB komut dosyalarını kullanarak bir AM test sinyali oluşturmak için bir dizi test sinyali kaydedilir ve kullanılır. Sinyal, FPGA uygulamasının simülasyonunda ve testinde kullanılır. Simülasyon kodu, FPGA tabanlı SDR sisteminin VHDL tasarımında bir çerçeve olarak da kullanılır. Test ve simülasyon sonuçlarını analiz etmek ve bir karşılaştırma yapmak için başka bir MATLAB betiği yazılmıştır. İki sinyal üzerinde yapılan bu testlerden elde edilen sonuçlar, daha yüksek SNR oranı daha iyi anlamına geldiğinden, sinyal A1 ile yapılan testlerin A2 sinyali ile yapılan testlerden daha iyi olduğunu kanıtlamıştır. Gerçek gerçek dünya değerleri her bir test sinyali için simülasyonlarla karşılaştırılırken, gerçek dünya SNR sonuçlarının simülasyon SNR'sinden biraz daha düşük olduğu not edilir. Test sonuçlarının, bir AM alıcısı için kabul edilebilir bir düzey olan 20dB'den daha yüksek bir SNR sağlaması durumunda. Test ve simülasyon sonuçları, FPGA AM RX sisteminin AM demodülasyonu ve alımı için yararlı bir aday olduğunu kanıtladı. Tasarlanan ve uygulanan FPGA AM RX sistemi, bu çalışmanın ana odak noktası olan temel SDR ilkelerinin eğitiminde de iyi bir yardımcı programdır.

Anahtar Kelimeler : SDR, FPGA, VHDL, SNR, MATLAB, RX, AM.Bilim Kodu : 90523

# ACKNOWLEDGMENT

I would like to express my appreciation to my great supervisor, Assist. Prof. Dr. Bilgehan ERKAL who has given me an unlimited support and valuable guidance. There are no enough words to express thanks to him.

As well as, I would like to thank my lovely family from my heart for their being with me by supporting me with all possible means.

# CONTENTS

| APPROVAL                       | ii   |

|--------------------------------|------|

| ABSTRACT                       | iv   |

| ÖZET                           | vi   |

| ACKNOWLEDGMENT                 | viii |

| CONTENTS                       | ix   |

| LIST OF FIGURES                | xii  |

| LIST OF TABLES                 | xiv  |

| SYMBOLS AND ABBREVITIONS INDEX | xv   |

| CHAPTER 1                      |      |

| INTRODUCTION                   | 1    |

| CHAPTER 2                      | 6    |

| SOFTWARE DEFINED RADIO (SDR)   | 6    |

| 2.1. SDR ADVANTAGES            | 6    |

| 2.2. SDR DISADVANTAGES         | 7    |

| 2.3. IDEAL SDR DESIGN          | 7    |

|                     | • • |

|---------------------|-----|

| ΓΙΟΝ AND OBJECTIVES | . 8 |

| DWARE               | . 8 |

| tional Receiver     | . 8 |

| EIVER               | 10  |

| NSMITTER            | 11  |

| CHAPTER 3                             | . 12 |

|---------------------------------------|------|

| FIELD PROGRAMMABLE GATE ARRAYS (FPGA) | . 12 |

| 3.1. FPGA ARCHITECTURE                | . 13 |

| 3.1.1. Logic Cells                    | . 15 |

# Page 1

| CHAPTER 4                                           | 17 |

|-----------------------------------------------------|----|

| AMPLITUDE MODULATION (AM)                           | 17 |

| 4.1. DOUBLE SIDE BAND AMPLITUDE MODULATION (DSB-AM) | 18 |

| 4.2. DSB-AM RECEIVERS                               | 18 |

| 4.2.1. Modulation Spectrum                          | 19 |

| 4.2.2. Demodulation Methods                         | 20 |

| 4.2.2.1. Envelope Detector                          | 20 |

| 4.2.2.2. Square Law Detector                        | 22 |

| CHAPTER 5                                     | . 24 |

|-----------------------------------------------|------|

| VHDL –HARDWARE DESCRIPTION LANGUAGE           | . 24 |

| 5.1. VHDL CONCEPTS                            | . 24 |

| 5.1.1. Behavoaral Modelling                   | . 24 |

| 5.1.2. Structural Modelling                   | . 25 |

| 5.1.3. RTL (Register Transfer Level) Diagrams | . 26 |

| 5.2. VHDL DESIGN STAGES                       | . 26 |

| 5.2.1. Entity                                 | . 26 |

| 5.2.2. Architecture                           | . 26 |

| 5.2.3. Package                                | . 27 |

| 5.2.4. Process                                | . 27 |

| 5.3. VHDL MODELLING BASICS                    | . 27 |

| 5.3.1. Constants                              | . 27 |

| 5.3.2. Signals                                | . 28 |

| 5.3.3. VHDL Operators                         | . 28 |

| 5.3.4. Concurrent Signal Assignments          | . 29 |

|                                               |      |

| CHAPTER 6                                        | 30 |

|--------------------------------------------------|----|

| FPGA BASED AM RECEIVER DESIGN AND IMPLEMENTATION | 30 |

| 6.1. HARDWARE COMPONENTS                         | 30 |

| 6.1.1. MIMAS - Spartan 6 FPGA Development Board  | 32 |

| 6.1.1.1. Introduction                            | 32 |

| 6.1.1.2. Applications                            | 33 |

| 6.1.1.3. Board Features                          | 33 |

# Page 1

| 6.1.2. LM4550 Audio Expansion Module                          |    |

|---------------------------------------------------------------|----|

| 6.1.2.1. Introduction                                         |    |

| 6.1.2.2. Applications                                         |    |

| 6.1.2.3. Board Features                                       |    |

| 6.1.3. IO Breakout Board                                      |    |

| 6.1.3.1. Introduction                                         |    |

| 6.1.3.2. Board Features                                       |    |

| 6.2. PROGRAMS                                                 |    |

| 6.2.1. Matlab                                                 |    |

| 6.2.2. HDSDR                                                  |    |

| 6.2.3. Audacity                                               |    |

| 6.3. MATLAB SIMULATIO CODES                                   |    |

| 6.4. VHDL CODE AND BLOCK SCHEMA OF THE SYSTEM                 |    |

| 6.5. RTL DIAGRAMS OF THE SYSTEM                               |    |

|                                                               |    |

| CHAPTER 7                                                     |    |

| RESULTS AND DISCUSSION                                        |    |

|                                                               |    |

| CHAPTER 8                                                     |    |

| CONCLUSION                                                    |    |

|                                                               |    |

| REFERENCES                                                    | 40 |

| REPERENCES                                                    |    |

|                                                               |    |

| APPENDIX A. DATASHEETS OF ELECTRONIC COMPONENTS<br>6, LM4550) |    |

| APPENDIX B. MATLAB CODE LISTINGS                              |    |

| APPENDIX C. VHDL CODE LISTINGS                                |    |

|                                                               |    |

|                                                               |    |

| RESUME                                                        |    |

# LIST OF FIGURES

| <u>Pa</u>                                                                                                                                                                                     | age  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.1. Functional block diagram of wireless communication system                                                                                                                         | 7    |

| Figure 2.2. Internal blocks of super heterodyne receiver                                                                                                                                      | 9    |

| Figure 2.3. Block diagram of the SDR receiver                                                                                                                                                 | 10   |

| Figure 2.4. Block diagram of a SDR transmitter.                                                                                                                                               | 11   |

| Figure 3.1. Internal structure of FPGA.                                                                                                                                                       | 13   |

| Figure 3.2. Basic FPGA architecture.                                                                                                                                                          | 14   |

| Figure 3.3. Contemporary FPGA architecture                                                                                                                                                    | 15   |

| Figure 3.4. Logic cells.                                                                                                                                                                      | 16   |

| Figure 4.1. Representation of the AM principle.                                                                                                                                               | 17   |

| Figure 4.2. Spectra of double-sided for AM signals and baseband.                                                                                                                              | 20   |

| Figure 4.3. The simple circuit of envelope demodulator                                                                                                                                        | 21   |

| Figure 4.4. A Signal and its envelope detector.                                                                                                                                               | 22   |

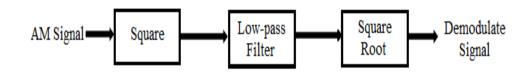

| Figure 4.5. Block diagram for squaring law.                                                                                                                                                   | 23   |

| Figure 6.1. General view of FPGA AM receiver.                                                                                                                                                 | 30   |

| Figure 6.2. Photo of the FPGA AM receiver.                                                                                                                                                    | 32   |

| Figure 6.3. Mimas – spartan 6 FPGA development board.                                                                                                                                         | 33   |

| Figure 6.4. LM4550 AC'97 audio expansion module.                                                                                                                                              | 34   |

| Figure 6.5. IO Breakout module for mimas                                                                                                                                                      | 35   |

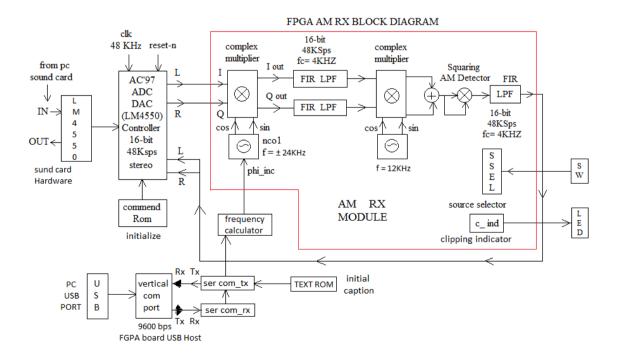

| Figure 6.6. Block schema of the FPGA AM RX system.                                                                                                                                            | 38   |

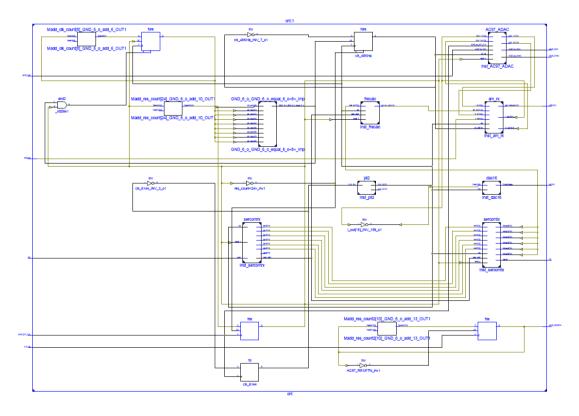

| Figure 6.7. RTL schematic of top module cnt.                                                                                                                                                  | 41   |

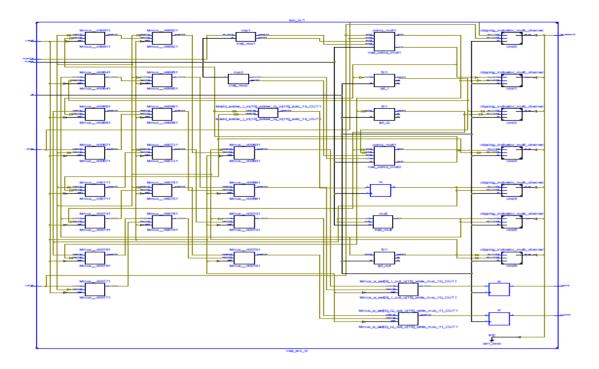

| Figure 6.8. RTL schematic of am_rx module.                                                                                                                                                    | 42   |

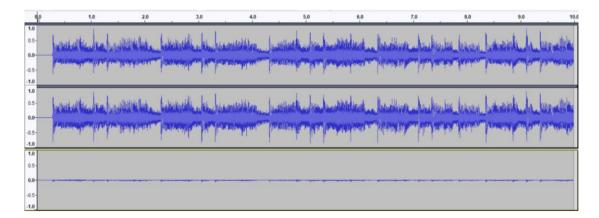

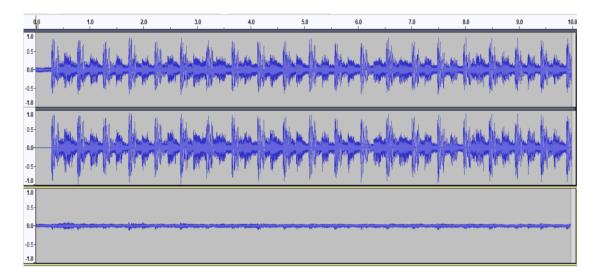

| Figure 7.1. FPGA AM RX system test results with A1 test signal: top signal is output demodulated waveform, middle test signal A1 at the input and the bottom signal is difference between two | . 44 |

| Figure 7.2. Matlab simulation results with A1 test signal: top signal is output demodulated waveform, middle test signal A1 at the input and the bottom signal is difference between two      | . 44 |

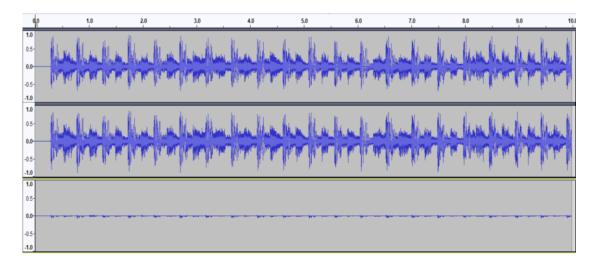

| Figure 7.3. FPGA AM RX system test results with A2 test signal: top signal is output demodulated waveform, middle test signal A2 at the input and the bottom signal is difference between two | . 45 |

# Page

| Figure 7.4. Matlab simulation results with A2 test signal: top signal is output |    |

|---------------------------------------------------------------------------------|----|

| demodulated waveform, middle test signal A2 at the input and the                |    |

| bottom signal is difference between two                                         | 45 |

# LIST OF TABLES

Page 1

# SYMBOLS AND ABBREVITIONS INDEX

### **ABBREVITIONS**

- AM : Amplitude Modulation

- FM : Frequency Modulation

- SDR : Software Defined Radio

- DSP : Digital Signal Processors

- FPGA : Field Programmable Gate Arrays

- RF : Radio Frequency

- IF : Intermediate Frequency

- DSB : Double Side Band

- DUC : Dynamic Update Client

- DUC : Digital Up Conversion.

- DAC : Digital-to-Analog Converter

- PLL : Phased Locked Loop

- ADC : Analog to Digital Converter

- ASIC : Application Specific Integrated Circuit

- DDC : Digital Down Converter

- HDL : Hardware Description Language

- LUT : Look Up Table

- RAM : Random Access Memory

- VHSIC : Very High Speed Integrated Circuit

- VHDL : VHSIC Hardware Description Language

- PCB : Printed Circuit Board

- FF : Flip-Flop

- IC : Integrated Circuit

- PLD : Programmable Logic Device

- CLB : Configurable Logic Blocks

- RTL : Register Transfer-Level

# **CHAPTER 1**

#### **INTRODUCTION**

Since the emergence of cellular communication in the last two decades, wireless communication channels gained more popularity. Currently, the development of wireless applications and wireless technology needs flexibility in the hardware. It is time-consuming and so expensive to make new radios in response to the change of wireless applications and standards [1]. These problems can be solved through software radio by moving the components of analogs to the digital domain. Functions of radio can be implemented by using programmable logic devices including Field Programmable Gate Arrays (FPGAs).

FPGAs offer the ability to implement functions in a cheap way which were previously implemented by using the components of analog hardware. They are constructed by one basic reconfigurable logic cell that doubled thousands of times. FPGAs are used as co-processors to interact with DSPs and general-purpose processors and offering lower cost and higher performance to the system. The freedom to select where to implement the baseband-processing algorithms will add another flexibility dimension when using Software Defined Radio (SDR) algorithms. Therefore, with SDR, it is possible to implement simply the radio communitarian process. We can say that SDR is better than the conventional radio communication system because with SDR all hardware is removed and replaced by pure software.

Moreover, this flexibility gives an advantage to SDR receiver where it will be able to decode the entire signals.

Besides, software radio permits a single device on receiving numerous and different wireless transmissions. By the use of digital signal processing mechanisms of FPGAs, the software radio may be accomplished in the digital systems. Nevertheless,

it is logical to focus on AM transmission rather than FM because constructing AM receiver is very easy to be learned. This technique is beneficial because it develops digital design mechanisms that can be applied in more advanced communication systems. Besides, implementing AM receiver by the use of analog electronics is always the base. Nevertheless, the development of digital systems allows the emulation of analog with digital circuity easily. The digital AM Receiver is a digital system that tries to accomplish the same analog AM receiver functions by using only FPGA and a small number of analog electronics.

In general, AM is a technique that is used to modulate the wave based on changing its amplitude based on changes in the frequency and amplitude together of the associated modulating signal and keep the frequency of the wave constant. The change in wave amplitude is directly associated with the change in the modulating signal amplitude. The changes in the modulating signal determine the positive and negative peaks of the wave change. Increase or decrease the modulating signal amplitude causes an associated increase or decrease of the wave peaks amplitude [2].

# **1.1. LITERATURE REVIEW**

In 1894-5, Marconi, Oliver Lodge and Alexander Popov invented the first radio receiver by the use of a primitive radio wave detector named as a cohered and invented in 1890 by Eduard Branly and improved by Lodge and Marconi [3]. At the beginning, it has high resistance. When the voltage of radio frequency was applied to the electrodes, its conducted electricity and resistance has been reduced. The coherer in the receiver was directly connected between the ground and antenna. Moreover, the coherer was connected to a DC circuit with a relay and battery besides its connection to the antenna. When the coherer resistance is reduced by the incoming radio wave, the current of battery flowed through it turning on the relay to ring a bell or create a mark on the tape of paper in the siphon recorder.

For restoring the coherer to the previous no conducting status in order to receive the next pulse of radio waves, it had to be tapped mechanically to disturb the metal particles [4]. This has been performed by a "DE coherer", and it is a clapper struck

the tube and operate by the electromagnet powered by a relay. In 1970, a researcher coined the term of "digital receiver". The Gold Room Laboratory in California generated an analysis of software baseband tool named Midas that was of course a software defined. In 1984, a team in Garland, Texas Division of E-Systems was coined the term "Software Radio". The same place witnessed the development of the 'Software Radio Proof-of-Concept' laboratory which published the software radio inside many governmental organizations. This software radio which has been invented in 1984 was a digital baseband receiver which offered programmable interference cancellation and demodulation for broadband signals, typically with thousands of adaptive filter taps by the use of many array processors retrieving shared memory. In 1991, the term 'software radio' has been reinvented by Joe Mitola independently in a plane to construct a GSM base station which may combine between Ferdensi's digital receiver with E-Systems Melpar's which control digitally the communications jammers to a true software-based transceiver.

The first main push in SDRs development is implemented by the use US military paper called SpeakEasy. The main objective for SpeakEasy paper was to use the programmable processing to simulate more than 10 presenting military radios which operate in frequency bands between 2 and 2000 MHz. The other design goal was to be able to easily include a new modulation and coding criteria in future. Therefore, the military communication can keep pace with the developed modulation and coding techniques. From 1992 to 1995, the main goal was to create a radio for the U.S. Army which would operate from 2 MHz to 2 GHz with satellites, Naval Radios, Air Force radios and ground force radios.

The main goal was to obtain a quicker reconfigurable architecture at open software architecture with cross channel connectivity (the radio may bridge various protocols of radio).

Harnani Hassan et al [5], from University Teknologi MARA implemented a low complexity SDR using Simulink, Matlab and Xilinx environment based on FPGA. Xilinx has been used as a platform used as a method for FPGA design whereas the Matlab and Simulink has been used to create a random spectrum signal. The methodology and mechanisms of the proposed transceiver design helped to design the SDR by offering a quick method altering system with low complexity. As well as, it opened the way to integrate cognitive radio aspect to wireless network including 3G and 4G in the future. As well as, the proposed design accomplished the goal and proved that it can be easily conducted by the use of Blockset, Xilinx DSP and Simulink. This design method provide a benefit to designers on using either HDL, Verilog or Matlab. As well as, it helped designers to determine the problems and provide a quick method to alter the system.

Shahana K et al [6], designed and implementation of Low Frequency Trans-Receiver on Spartan-3AN device. System Generator has been used to design and to simulate system level models, and to get the timing and resources using results before conducting the design on actual device. The primary idea behind this is to seek about the feasibility to get the software close to the antenna as can as possible and therefore, solve the problems of hardware by using software. The benefit of this method is that the equipment is relatively cheap and more versatile. Also, the low frequency trans-receiver based on FPGA is simple to be upgraded and offers high flexibility in execution. The measured findings shown that the input of transmitter matches with the output of receiver. Furthermore, Simulation of Matlab has been implemented for further aware to the mentioned problem. The comprehensive implementation is considered a perfect example to conduct the problem of hardware in software. In addition, it offers low power solution and low cost. FPGA implementation may further deliver flexibility to customize the design on different data ratios, Carrier Frequency, Filter types, Modulation types, etc. which make the design efficiently reconfigurable.

Jiang-tao Gong et al [7], from Hunan Railway Professional Technology College presented the block diagram for FPGA to realize the distributed algorithm which can implement the SDR channel processing, where it consists a multiple FIR filters bank for various frequency bands because the radio system defined by a software need into a series of different FIR filters to catch the equivalent signal. Through the distributed algorithm depending on signal processing structure of FPGA and by Repeating configure the FPGA, it may accomplish more FIR filter bank switching, in order to accomplish different channel information receiving. It offers applicable processing approaches and thoughts for radio channel switching defined by software.

In this study, an AM receiver using SDR techniques is designed and implemented in FPGA on Spartan 6 FPGA Board with LM4550 Audio and IO Breakout Board. The basic notion behind is to seek provide a cheap and simple FPGA based platform for teaching and learning of SDR basics. Where a simulation environment is set using MATLAB scripts. And a set of test signals are recorded and used to generate an AM test signal using MATLAB scripts. The signal is used in simulation and test of FPGA implementation. Simulation code is also used as a framework in the VHDL design of the FPGA based SDR system. Another MATLAB script is written to analyze the test and simulation results and make a comparison.

Test and simulation results prove FPGA AM RX system a useful candidate for AM demodulation and reception. Subsequently the designed FPGA AM RX system a good in the education of basic SDR principles. Also it can be used in teaching the radio signal processing techniques using FPGAs. The system is also suitable to be used with any soundcard based SDR frontend.

# **CHAPTER 2**

#### SOFTWARE DEFINED RADIO (SDR)

Radio development in the communication field which people need, comprising video and voice communication and broadcasting messages, etc. Radio SRD is the definition of system software that comprises the entire or many descriptors including modification, extraction, and others. Wireless devices are used easily and cost less business mission. Software-defined radio (SDR) provides many advantages where it pushes forward the cost of communication and flexibility with several advantages accomplished by the service providers to the end-users. You can obtain more than an explanation for the software-defined Radio also called (SDR). Radio is a wireless device that sends information and receives frequencies. Many issues must be solved in order to access SDR including tuning the specification of the system according to numerous applications. We may return some of all will be held including modification, extraction and encoding. To end it, this information helps the recognition of these specifications through the reception [8].

# 2.1. SDR ADVANTAGES

- Point and Click Control

- Easy Tuning

- A Computer Is Sharing the Workload

- Cheaper (In Some Cases)

- Smaller

- Visual look at a signal

- Open Platforms

- Custom Filtering Uses modern technology

#### 2.2. SDR DISADVANTAGES

- Filtering Traded For Space

- Hard to run on old computers

- Sending is more expensive

- Dependent on Computer

- Software Limits

## 2.3. IDEAL SDR DESIGN

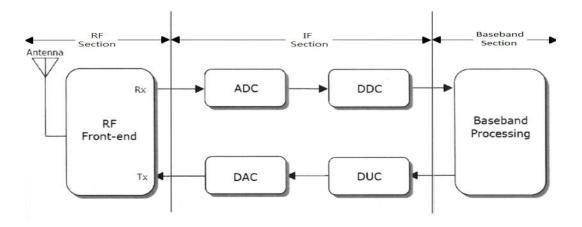

Software-defined radio system (SDR) is considered one of the most significant contemporary techniques in supporting the communication in military service insecurity, war and peace. SDR is used rather than the conventional radio and it involves optimal radio frequency RF convertor wireless signal to an analog IF properly used in conventional radio. Analog signal conversion to a digital frequency (ADC) in IF and convert the signal from digital to analog FM frequency in the IF is called (DAC) and shown in Figure 2.1.

The transfer of the signal routed by the converter sample rate by the interface (ADC) and the treatment of hardware in the receiver. SDR may use the processing of baseband with several digital devices including digital signal processors (DSP) and field-programmable gate arrays (FPGA).

Figure 2.1. Functional block diagram of wireless communication system.

There are many advantages to the use of digital devices such as low energy consumption, high processor speed and flexibility. Nevertheless, there is a comparison between the extreme flexibility degrees with the increase in consumption of energy for DSP to minimum limit the flexibility and lower consumption of energy than ASICs. FPGA provides astray consistent devices that cheap and less energy consumption than DSP and ASICs flexibility FPGA and the redesign is made it optimal of SDR [9].

## 2.4. MOTIVATION AND OBJECTIVES

SDR looks like many technologies in terms of its development and it is used in both military and civilian applications and called Speakeasy. It is used in the naval forces of the United Stated between 1991-1995. This technology accomplished great success in the basic rules, knowledge, radio program, wireless communication and programming. Currently, all SDR software is available at low prices [10].

#### 2.5. SDR HARDWARE

#### 2.5.1. Traditional Receiver

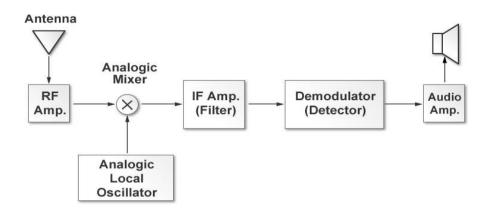

In addition to the classic demodulation, the traditional receiver and the three processes to determine the sign in the carrier frequency setting of frequency shifting, the candidate is filtering or separated from others. The compensation for transport losses by enlargement is inserted enlargement by mass demodulation. Because of carrying the signal to the demanded level circuit demodulation, most of the conventional reception setups use different plans for about a century. Figure 2.2 shows the basic structure is significant to differentiate between the conventional and reception by new SDR methods.

Figure 2.2. Internal blocks of super heterodyne receiver.

Figure 2.2 clarifies the signal interference by the antenna. The signal is amplified during RF phase that works in the frequency area of benefit only after passing the reference to the mixer during the other input which receives the contribution oscillator ornament and appointing local frequency oscillator. By tuning the radio which is responsible to translate the frequency signal mediator (IF), the mixer is responsible for shifting the frequency to the medium frequency IF.

The purpose of appointing a frequency oscillator is to confirm that the amount of time difference frequency signal is equal to (IF). For instance, if the frequency at the FM station is 100.7 MHz and IF was rumored to 10.7 MHz, the oscillator should be adjusted to 90 MHz situation due to the low side transformation. The following phase is the phase of weakening all the candidate wave signal but certainly a part of the spectrum. The received signal of the band is prevented to display by the bandwidth. At the end of the stage, the original signal modified is restored by the demodulator through the loudspeaker IF it uses one substitute. To increase the processing of the signal, it depends on the purpose through which its intended recipient device. Cross of information learned to a loudspeaker connected to the speaker [11, 12].

# 2.6. SDR RECEIVER

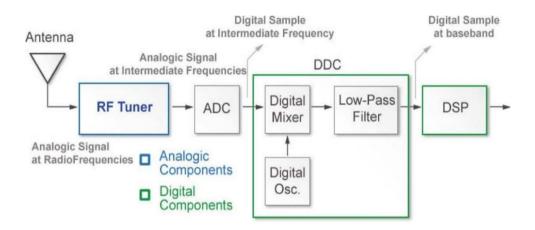

Figure 2.3. Block diagram of the SDR receiver.

Figure 2.3 for receiver signal SDR and be the first fund pass it RF tuner transfers the analog signal to IF to be the same and conduct the process in the first three boxes of the variant receiver device to the convergence point of the two systems [13].

Then cross-reference IF are changed frequency band by ADC is liable on change and is fed into the next phase and be down the digital converter. DDC is a significant part of the SDR system, it is cheap and consists of three main parts as follows:

- Digital local oscillator.

- Digital mixer.

- Finite pulsation response FIR low-scrolling IF filter.

Reference transfers to the corresponding baseband in our digital mixer at the counter of phase elements by the analysis [14]. It is a modified digital local oscillator that the reference is needed far or up to 0Hz and the difference with the bandwidth along and be a low-pass filter and detects any receiver part is a suitable signal. Another approach is represented by decreasing the sampling ratio or sampling frequency is taken to new samples from the baseband and create from the split in the frequency of the original sample through an N element. It is named the decimation element. The ratio of the end sample may be less than double the higher-frequency elements by Nyquist theory. The samples crossing to the baseband digital signal processing in a DSP box, finally, for example decoding and demodulating [15].

# 2.7. SDR TRANSMITTER

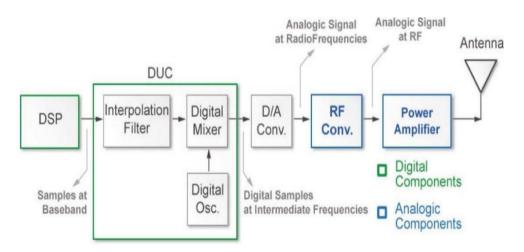

As shown in Figure 2.4, DSP income generates the baseband signal to be sent by SDR. The first box is DUC for digital transformation and translates the baseband signal for IF by make its passband.

DAC send the samples to the field analog after the RF is moving towards the highfrequency signal is later enlarged and the signal transmitted from the antenna DUC Filter is responsible for the high sample ratio of the baseband signal which is compatible with the operating of the elements followed by the so reverse process arises at the reception frequency [14, 15].

Figure 2.4. Block diagram of a SDR transmitter.

# **CHAPTER 3**

#### FIELD PROGRAMMABLE GATE ARRAYS (FPGA)

FPGA can be described as a device that includes a matrix of reconfigurable gate array logic circuitry. When FPGA is formed, the internal circuitry is connected in a method that produces a hardware implementation of the software application. FPGAs do not include an operating system and they use dedicated hardware to process logic. The nature of FPGAs is parallel and therefore, different operations are not competing for the same resources. Consequently, when adding additional processing, one part of the application performance is not influenced.

Besides, many control loops can operate on a single FPGA device at different ratios. The critical interlock logic can be enforced by FPGA-based control systems and can be designed to inhibit I/O enforced by the operator. Nevertheless, FPGA-based systems are unlike the hard-wired printed circuit board designs that have stable hardware resources where FPGA-based systems may rewire their inner circuitry to help the reconfiguration when the control system deploys in the field.

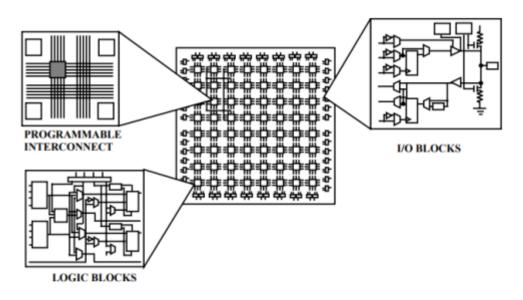

FPGA offers the reliability and performance for the dedicated hardware circuity. By the use of FPGA, it is possible to substitute thousands of discrete elements by merging millions of logic gates in one integrated circuit (IC) chip. As shown in Figure 3.1 the internal resources of FPGA chip include a matrix of configurable logic blocks bounded by a periphery of I/O blocks. Inside the FPGA matrix, the signals are routed by wire routes and programmable interconnect switches.

Figure 3.1. Internal structure of FPGA.

# **3.1. FPGA ARCHITECTURE**

The FPGA structure consists of many components as follows:

- Look-up table (LUT): This component conducts many logical operations.

- Flip-Flop (FF): This register component stores LUT result.

- Wires: These components connect components.

- Input/output (I/O) pads: These ports are physical and their mission is to get data in and out of FPGA.

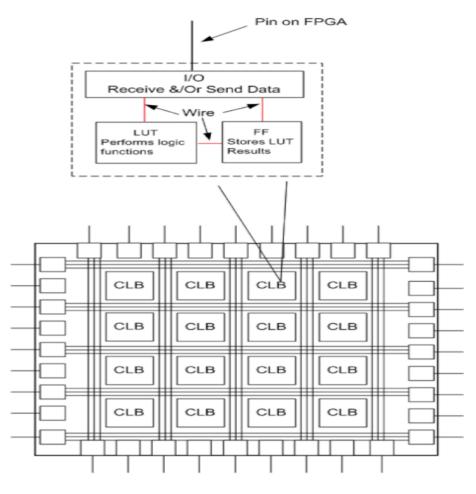

The collection of these components produce the basic structure of FPGA as clarified in Figure 3.2. Despite the efficiency of this structure to implement any algorithm, the proficiency of the resulting implementation is limited in terms of calculated output, feasible clock frequency and demanded resources.

Figure 3.2. Basic FPGA architecture.

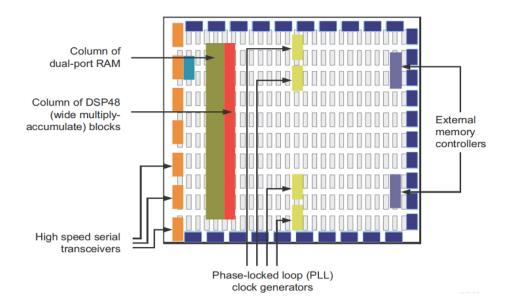

The modern architecture of FPGA includes many basic components accompanied by other computational and storage blocks which increase the effectiveness and computational density of the device. The additional components which will be discussed in the following sections are as follows:

- Embedded memories to store the distributed data.

- Phase-locked loops (PLLs) to drive the FPGA fabric at different clock ratios.

- High-speed serial transmitting and receiving devices.

- Off-chip memory controllers

The collection of these components gives FPGA the flexibility in implementing any software algorithm running on processors and produce the modern FPGA architecture shown in Figure 3.3.

Figure 3.3. Contemporary FPGA architecture.

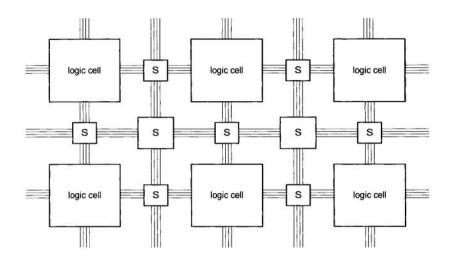

# 3.1.1. Logic Cells

The simple FPGA includes a large number of logical cells and each cell can be configured to conduct many functions. Each logic cell has a unified number of entries and exits. The logic cells used in FPGAs are as follows:

- Multiplexer based logic cells (e.g. Actel FPGAs)

- Memory-based logic cells (e.g. Xilinx FPGAs)

The basic internal structure of FPGA in a very wide sense is shown in Figure 3.4.

Figure 3.4. Logic cells.

As shown in Figure 3.4 that the internal structure of FPGA consists of programmable interconnections and configurable logic cells.

# **CHAPTER 4**

#### **AMPLITUDE MODULATION (AM)**

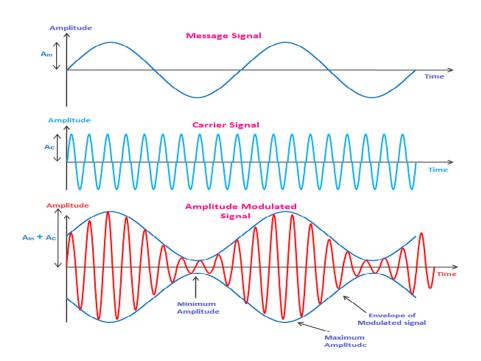

The amplitude modulation occurs when high-frequency carrier wave amplitude differs as a function of signal intensity. Figure 4.1 shows the principle of amplitude modulation. We can realize that the amplitudes of positive and negative carrier wave half-cycles differ in relation to the signal. This means that increasing the positive sense results lead to an increase in the carrier wave amplitude whereas the opposed happens for the negative half-cycle. In general, AM process is implemented by the use of an electronic circuit which is called a modulator [16].

Figure 4.1. Representation of the AM principle.

The AM process includes an important consideration which is the modulation factor. We can imagine this factor as the depth of modulation or change in carrier amplitude. In other words, it represents the ratio between the change in carrier amplitude and the amplitude of normal carrier wave. The purpose of this factor is the determination of strength and quality of transmitted signals respectively. The modulation of the carrier in AM wave to a small degree produces a small change in carrier amplitude. Therefore, the transmitted audio signal is not too strong. This means that the audio signal is stronger and clearer when the modulation degree is great [16].

#### 4.1. DOUBLE SIDE BAND AMPLITUDE MODULATION (DSB-AM)

One of the main types of AM technique is Double Side Band (DSB) where DSB consists of two sidebands upper and lower with wave carrier suppressed. Practically, DSB is consistent with SSB receivers where the last one is considered of the main types of AM techniques in which the receiver rejects only the unwanted or redundant sideband.

DSB signals are generated based on suppressing the carrier that results in the upper and lower sideband. This generating method does not consist of waste in power.

DSB signal is generated based on modulating a carrier across the information signal of a single-tone sine wave and signifies the summation of two sinusoidal sidebands. Later, the carrier suppressed and the amplitude of the DSB sine wave signal changes in the frequency of the carrier. The main features of DSB signal are the transition of the stage that occurs at the wave lower amplitude slices. In general, DSB carrier signals are generated by the balanced modulator circuit based on generating the difference or summation between frequencies and to cancel or balance the carrier. However, DSB signals are rarely used despite these features and both the low cost and simple design because it is difficult to demodulate signals at the receiver. DSB signals are used in many applications but the most important one is the transmitting of information in television signals [17].

# 4.2. DSB-AM RECEIVERS

One of the oldest radio modulation technique is the amplitude modulation. The receivers which are used to listen to DSB-AM are maybe the simplest receivers for

any radio modulation technique that perhaps the reasons behind the use of this versions of amplitude modulations until now. The super heterodyne type of receivers is the most popular receivers in use currently. They comprise of Amplifier, Local Oscillator and Mixer, IF Section, Antenna, and Detector RF amplifier. The need of these systems can be noticed when we consider the simplest and inadequate TRF or tuned radio frequency amplifier. Amplitude modulation happens when the carrier wave amplitude is modulated in order to respond to the source signal. In amplitude modulator, we have an equation which is look this:

$$A_{signal}(t) = A(t)\sin(\omega t) \tag{4.1}$$

As where the much simple form amplitude modulation modulator comprises of a diode that is configured to represent a detector of envelop. Product detector is considered another type of demodulator which provide better-quality demodulation with further circuit complexity.

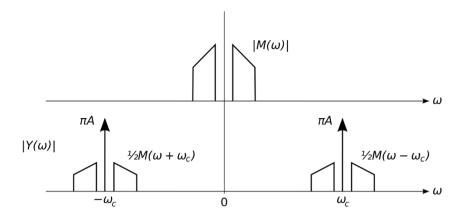

#### 4.2.1. Modulation Spectrum

As treated previously, the beneficial modulation signal m(t) is frequently more complicated than a single sine wave. Nevertheless, in accordance with Fourier decomposition, m(t) can be convoyed as the set of sine wave sum for many stages, frequencies and amplitudes.

By performing the multiplication of 1 + m(t) with c(t) as previously, the result comprises a sum of sine waves. The carrier c(t) presents unchanged, but every frequency element of m at  $f_i$  has two sidebands at frequencies  $f_c + f_i$  and  $f_c - f_i$ . The set of previous frequencies above the carrier frequency is called as upper sideband and those lower configure the lower sideband. As clarified in upper of Figure 2, the modulation m(t) can be considered to comprise an equal combination of positive and negative frequency factors. The sideband can be viewed as the modulation m(t) which is simply shifted in frequency by  $f_c$  as showed at the bottom from the right of Figure 2.

Figure 4.2. Spectra of double-sided for AM signals and baseband.

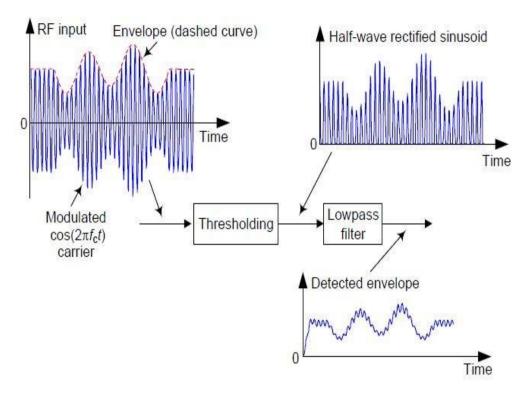

# 4.2.2. Demodulation Methods

The simplest type of amplitude modulation comprises a diode that is configured to represent an envelope detector. Product detector is considered other type of demodulator that has the ability to offer better-quality demodulation with further circuit complexity.

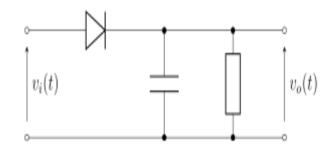

# 4.2.2.1. Envelope Detector

When there is an attempt to demodulate the modulation amplitude, it looks like a good sense which only the amplitude of the signal need to be cheeked. By checking only the amplitude of signal at specific time, it is possible to eliminate the carrier signal from consideration and it is possible to check the original signal. The amplitude of signal can be checked by using a tool in our toolbox (the envelop detector).

The envelope detector is just a half wave rectifier followed by a low pass filter. It can be imagine as electronic circuit which takes (comparatively) high-frequency amplitude modulated signal as input and delivers an output that is the demodulated envelop of the original signal as shown in Figure 4.3.

Figure 4.3. The simple circuit of envelope demodulator

The detector is placed after the IF section in case of commercial amplitude modulator. In this point, the carrier is 455 kHz whereas the highest frequency of envelop is only 5 kHz. Since the ripple element is about 100 times the frequency of the maximum baseband signal and does not pass through any succeeding audio amplifiers. We can see below the forms of AM or FM signal x(t) as follows:

$$x(t) = R(t)\cos(\omega t + \varphi(t))$$

(4.2)

In the case of AM,  $\varphi(t)$  (the stage element of the signal) is constant and can be neglected. Moreover, the carrier frequency  $\omega$  of amplitude modulator is also constant. Therefore, the entire information of the amplitude modulator signal is in R(t) where R(t) is known as the envelope of the signal. Thus, the amplitude modulator signal is given by the function as follows:

$$x(t) = (C + (mt))\cos(wt)$$

(4.3)

C represents the carrier amplitude, (mt) represents the original audio frequency message and R(t) equal to C + (mt). Consequently, the original message can be recovered if the envelop of the amplitude modulator is extracted.

Figure 4.4. A Signal and its envelope detector.

#### 4.2.2.2. Square Law Detector

A square low detector of electronic signal processing is a device which create an output relative to square of some input. For instance, in radio signal demodulation, semiconductor diode is used as a square law detector which provide an output existing relative to the square of the amplitude of the input voltage over some range of input amplitudes. A square law detector offers an output directly relative to the power of the input electrical signal. Moreover, square detector is a coherent or synchronous detector. It avoids the problem to recreate the carrier by simply square the signal of input. Basically, it uses the amplitude modulator signal itself as a range of wideband carrier. The multiplier output is the square of the input amplitude modulator signal:

$$(e_{am})^2 = (\sin \omega_c t + \frac{m}{2} \cos(\omega_c + \omega_m) t - \frac{m}{2} \cos(\omega_c + \omega_m) t)^2$$

$$(4.4)$$

Figure 4.5. Block diagram for squaring law.

#### **CHAPTER 5**

#### **VHDL – HARDWARE DESCRIPTION LANGUAGE**

VHDL is a term that refers to the Very high speed integrated circuit (VHSIC) Hardware Description Language (VHSIC). VHDL is a programming language used to describe the logic circuit by functioning the behavior of data flow and/or the structure.

The description of this hardware is used to configure a programmable logic device (PLD) including a Field Programmable Gate Array (FPGA) with a convention logic design. Also, VHDL is a formal language used to specify the structure and behavior of the digital circuit.

#### **5.1. VHDL CONCEPTS**

The goal of VHDL is to describe a model of digital hardware device where this model identifies the external view of the device and one or more of the inner views. The external view of the device identifies the interface of the device which it can communicate with many models in the same environment while the internal view of the device identifies the structure or functionality.

#### **5.1.1. Behavoaral Modelling**

The most basic formula for the behavioral modeling of VHDL is the signal assessment statement as shown in the following example:

a <= b;

The previous example means that a gets the value of b. This statement has an effect which is signal a is replaced by signal b. When the value of signal b is changed, this

statement is executed. The sensitivity list of this statement is signal b. The signal statement is executed when a signal in the sensitivity list of a signal assignment statement changes value. If the execution produced a new value that is different from the present value of the signal, the event will be scheduled for the target signal. Consequently, no event will be scheduled but the transaction is still generated if the execution result value is the same. The event is scheduled by only the changes of the value while the transaction is always generated when the model is assessed.

A transaction is always generated when a model is evaluated, but only signal value changes cause events to be scheduled.

#### 5.1.2. Structural Modelling

The structural description describes the logical elements of the system and thus, it is a simulation of the system. The elements can be OR gate(s), AND gate(s), or it can be at a higher logical level for example Processor Level or Register Transfer-Level (RTL). The structural description is more traditionally used than the behavioral description for the system which requires explicit design. If we want to operate A + B=C. In behavioral design, we must write C = A + B and we have no choice on the type of adders used to conduct this addition process.

The entire statements with the structural description are concurrent. The entire statements that have an event conducted concurrently through any simulation time.

The main difference between VHDL and Verilog structural description is the availability elements (particularly primitive gates) for the user. The whole primitive gates including AND, OR, XOR, NOT and XNOR are recognized in Verilog. The gates must be linked to library, packages or modules which have the description of gates to be recognized by the VHDL packages.

#### 5.1.3. RTL (Register Transfer Level) Diagrams

Register-transfer level (RTL) that existed in the digital circuit design is modeling the asynchronous digital circuit in terms of digital signals flow between the logical operations conducted on those signals and hardware registers. Register-transfer level abstraction is used hardware description languages (HDLs) such as Verilog and VHDL to generate high-level illustrations of a circuit through which lower-level representations and at the end actual wiring are derived. RTL design is considered a distinctive practice for modern digital design [18].

In contrast with software complier design when register-transfer level intermediate exemplification is the lowest level, RTL level is the ordinary input which designers of circuit operate on there are various more level than it. Actually, in the synthesis of the circuit, a transitional language is used between input register transfer level representation and target netlist. Unlike in netlist, constructs for example cells, functions and multi-bit registers are existed [18].

#### 5.2. VHDL DESIGN STAGES

#### 5.2.1. Entity

Entire designs are expressed in terms of entities. The most basic building block of design is the entity. The entity of VHDL determines the entity name, entity ports and information related to the entity. Entire designs are created by the use of one or more entities [19]. If the type of design is hierarchal, the description of the top-level will include a description of the lower-level contained in it.

#### 5.2.2. Architecture

The architecture description is included in all entities which can be simulated. The behavior of the entity is described by the architecture. Multiple architectures are included in a single entity a single architecture might be structural while another architecture might be a behavioral description of the design.

#### 5.2.3. Package

The main goal of the package is to encapsulate the elements which can be shared (globally) between two or more design units. A package is a popular storage unit that can be used to hold data to be shared between many entities. Data can be shared through packages where the declaration of data inside the package helps the data to be referenced by further entities.

Each package includes two parts: a package body and a package declaration section. The interface of the package is defined by the package declaration and looks like the same method in which the entity defines the model interface. The actual behavior of the package is specified by the package body in the same approach that the architecture statement does for the model.

#### 5.2.4. Process

The basic execution unit of VHDL is the process. The process can be categorized into single and multiple processes in the entire operations that are conducted in a simulation of a VHDL description.

#### **5.3. VHDL MODELLING BASICS**

#### 5.3.1. Constants

The constant objects are names given to a particular value of type. Constants provide the capability to have a well documented model and a model that is easy to update. For example, constants are used when a model needs the same value for several cases. The designer can change the value of the constant and compile which will change the whole cases of instances to reflect the new value of the constant.

#### 5.3.2. Signals

Models are formed by the connection of entities together by using signal objects. The communication of dynamic data between entities is implemented by signals. A declaration of the signal is written is as follows:

SIGNAL signal\_name: signal\_type [:= initial\_value];

Signal name(s) is followed by the keyword SIGNAL. A new signal is created by each signal name. A colon separates between the signal name and signal type. Type of signal refers to the type of information on which the signal consists.

The signal can include an initial value specifier through which the value of the signal can be initialized. It is possible to declare the signal in package declarations, architecture declarations and entity declaration sections. Signals declared in the package are referred to as global signals because they may be shared between entities.

#### 5.3.3. VHDL Operators

There are six categories of predefined operators in the language and these operators can be described as follows:

- Additional operators

- Multiplication operators

- Relational operators

- Logical operators

- Shift operators

- Miscellaneous operators

Each operator has increased precedence starting from the category (1) to (5). Operators located in the same classification have the same precedence and the evaluation is implemented from left to right. Left to right evaluation can be overridden by the use of parentheses.

#### **5.3.4.** Concurrent Signal Assignments

Each assignment statement in a typical programming language including C and C++ implements one after the other in identified order. The statement order of the source file determines the order of implementation. No specified ordering of the assignment statements inside VHDL architecture. The implementation order inside VHDL architecture is only specified by events occurring to signal which the assignment statements are sensitive to.

#### **CHAPTER 6**

#### FPGA BASED AM RECEIVER DESIGN AND IMPLEMENTATION

Design and Implementation of FPGA based AM receiver consists of three parts: selection of hardware design components, algorithmic design and simulation of software parts in MATLAB and actual implementation of VHDL source code in the FPGA for actual real world tests.

#### **6.1. HARDWARE COMPONENTS**

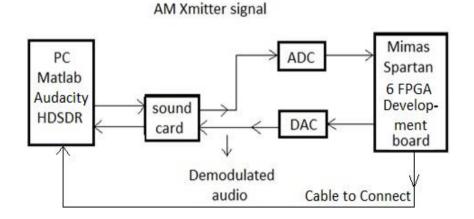

There are mainly three components in hardware part. MIMAS FPGA board, LM4550 soundcard and IO breakout board which adapts soundcard with PMOD connectors to the FPGA main board. Other than these three hardware components, there are interface cables: one USB-to-serial adapter cable for sending commands to the FPGA board, one USB cable for FPGA programming and two audio extension cables for connecting the analog sound input and outputs of LM4550 soundcard to the PC soundcard. The general view of the system is shown in Figure 6.1.

Figure 6.1. General view of FPGA AM receiver.

In Figure 6.1, a modulated signal produced by the Audacity played back way file which is produced using Matlab codes which will be defined later, is sent through PC's soundcard line-output to the line-in of FPGA's soundcard LM4550. The ADC of the LM4550 digitizes these audio signals in 16-bit, 48KSps, stereo format. The two channels of the stereo audio interface provides a means to represent a complex signal. So, the effective bandwidth of the AM radio signal is +24KHz as Nyquist criteria for sampling complex signals suggests. Thus the total bandwidth of the processed complex signal will be 48KHz. This complex signal which incorporates two DSB-AM stations where each one plays two 10 second duration of different music on two different frequencies continously, is processed and demodulated by the FPGA fabric which is programmed appropriately for this purpose. So, all the processing of the signal after digitization is carried on by FPGA fabric which can be redefined with software (VHDL in this case). Which of the two stations are selected is determined by a frequency setting command sent through the serial link provided by the virtual serial communication port. The demodulated signal is then sent through the DAC part of the LM4550 soundcard at 16-bits, 48KSps stereo format. Despite the fact that the uplink is a two channel stereo audio stream, the resulting signal is a mono signal in real format and this mono signal is simply repeated in the two channels. However, there is a source select module programmed in the FPGA, which takes commands through built-in switches on the FPGA mainboard and thus the stereo up-link is useful in representing the complex signals that the different part of FPGA AM RX module has. The source select module diverts the inter block signals to output according to the commands from the swtiches and gives the opportunity of seeing the different processing stages of the signal. Also, there is a clipping indicator module in the FPGA fabric, which shows the level (actually an indication of whether clipping occurs or not) of the signal at the input of every signal processing block in the AM receivver module. This indicator is useful in seeing that the level of the signal at the input of that stage is healthy or not. The clipping indicator module uses on-board LEDs for this purpose.

The resulting receiver signals are then monitored, recorded and analyzed at the PC using MATLAB scripts and HDSDR program which is a third party free SDR software used in amateur radio projects.

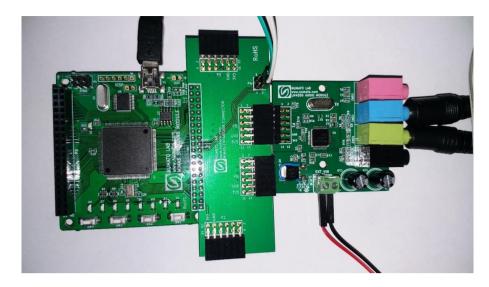

Figure 6.2. Photo of the FPGA AM receiver.

Shown in Figure 6.2 is a photo of the actual working prototype of the system. Here, connecting cables, LM4550 Audio extension card, IO breakout board and main FPGA board is clearly seen. Hardware components of the FPGA AM receiver are given in the next sections in detail.

#### 6.1.1. MIMAS - Spartan 6 FPGA Development Board

#### 6.1.1.1. Introduction

Mimas is easy to use the Development of FPGA board presenting Xilinx Spartan-6 FPGA. Mimas has been designed to learn and experiment design of the system with FPGAs.

This developed board presenting Xilinx XC6SLX9 TQG144 FPGA with a maximum of 70 user IOs.

The USB 2.0 interface offers easy and quick configuration download to the on-board SPI flash. There is no need for a special downloader cable or programmer to download a bitstream to the board [20].

Figure 6.3. Mimas – spartan 6 FPGA development board.

## 6.1.1.2. Applications

- Product Prototype Development

- Home Networking

- Signal Processing

- Wireless and Wired Communication

- An educational tool for university and school [20].

## 6.1.1.3. Board Features

- FPGA: Spartan-6 XC6SLX9 in TQG144 package

- Flash memory: 16 Mb SPI flash memory (M25P16)

- 100MHz CMOS oscillator

- USB 2.0 interface for On-board flash programming

- FPGA configuration via JTAG and USB

- 8 LEDs and four switches for user-defined purposes

- 70 IOs for user-defined purposes

- Onboard voltage regulators for single power rail operation [20].

## 6.1.2. LM4550 Audio Expansion Module

## 6.1.2.1. Introduction

This Audio module features LM4550, an audio codec for PC systems that is completely compliant and implements the analog concentrated functions of the AC'97 Rev 2.1 architecture. LM4550 uses 18-bit Sigma-Delta ADCs and DACs to create a high-quality stereo audio output [21].

Figure 6.4. LM4550 AC'97 audio expansion module.

#### 6.1.2.2. Applications

- Product Prototype Development

- Audio Record/Playback Systems

- Media players [21].

### **6.1.2.3. Board Features**

- One 2×6 pin Expansion connector

- AC'97 Rev 2.1 Compliant

- 90 dB Dynamic Range

- Stereo Headphone Amp With Separate Gain Control

- Dimension: 50mm x 46mm [21].

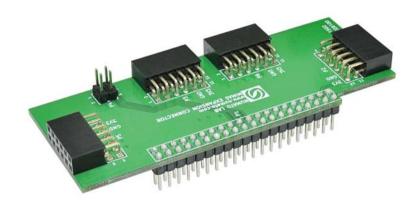

#### 6.1.3. IO Breakout Board

#### 6.1.3.1. Introduction

This product is an IO breakout solution for Mimas Sparta6 development board. This product helps Mimas IOs to be categorized into smaller 2x6 headers which may enable easy attachment for the other peripheral expansion modules. It features four  $2\times6$  extension connector [22].

Figure 6.5. IO Breakout module for mimas.

### 6.1.3.2. Board Features

- Four 2x6 pin expansion connector.

- Can be connected to any side of Mimas.

- Dimension: 34.3mm X 88.1mm [22].

### 6.2. PROGRAMS

In this study, third party software packages are used in the various stages. These programs and their role in the study are given in the next sections in detail.

#### 6.2.1. Matlab

The significance to use MATLAB in our study is that realistic implementation of SDR must include some equipment, for example, a high-speed A/D converter, a powerful signal processor. This equipment makes the hardware platform very expensive for students who study radio communication. Therefore, we used Matlab in our study and radio signal frequency is limited in the band of audio. One Matlab session has been through the setup of the receiver. Also, Matlab is used to complete all the modulation and demodulation studies. When this system is used, the user needs to only select the modulation and demodulation and corresponding factors.

#### 6.2.2. HDSDR

HDSDR is SDR program which is used to listen into radio, analysis of spectrum and analyse the results. It enjoys by waterfall and varied range separated from each other of the input and output signal. It prevent noise to accomplish the lower speed waterfall spectrum and receive and transmit the signals prepared by similar Matlab scripts. HDSDR monitors and records the waveform produced by PC's sound card. As well as, it works to record and playback RF, IF and AF WAV files with recording scheduler. Therefore, HDSDR software allows a user to enter the mode and global offsets to sync properly the pitch between the radio and SDR audio.

#### 6.2.3. Audacity

It is used as a recording and playback program. It can be used easily as a powerful audio editing and recording package. It allows to record voices and edit recorded voices to correct any mistakes in voices and to combine some sound recordings from many resources including music, interviews, or other recording of sound. Audacity allows to export the recordings in MP3 files format and because of this, it is suitable to produce podcasts.

#### 6.3. MATLAB SIMULATIO CODES

In the first place the test signal used in the experiments, which is played through PC soundcard using Audacity program is generated by the help of a MATLAB script. The code is listed in Appendix B.1. The code is very straightforward and comments in the code explains itself. The MATLAB program firstly takes two audio sample files in wave format which are prepared as 10 second duration mono music sampled at 8KSps format wave files. It up-samples and interpolates to 48KSps each and uses in the modulation of two different AM stations whose frequency is determined by the parameters in the code and so can be changeable. The resulting modulated waveform is complex thus it is recorded in stereo format. This sample signal is then used in both actual operational testing and MATLAB simulation of the system.

Another script is used to design filters used in the system and derived coefficients are then transferred to the FIR filter IP component through a coefficient file. The MATLAB script used for this purpose is listed in Appendix B.2. The program shows the frequency response of the designed filter as a graphic and stores the coefficients of the filter in a file which will be used in the FIR filter IP of the FPGA AM receiver. Here, number of the coefficients, sampling rate and cut-off frequency of the filter can be changed as desired.

The design of the algorithms underlying the principles of FPGA AM receiver and simulation of the system is achieved using a MATLAB script. Then, the algorithms are transferred to FPGA after recoded in VHDL. The VHDL codes of the FPGA AM receiver will be discussed later. The listing of the simulation code is given in Appendix B.3. This code is also very straight forward and explained by comment lines well. It takes test signal in wave file format, demodulates one of the AM stations whose frequency is set by a parameter in the code and using squaring method (envelope detection) demodulates, filters and records the resulting signal as a 48KSps mono wave file so that it can be played back and listened later. Also, products obtained at the various stages of demodulation process is recorded in separate wave files for seeing the evolution of the signal and further analysis purposes.

Lastly a MATLAB script listed in Appendix B.4 is used to compare the original modulating waveform with the demodulation result of the either simulation program or FPGA AM receiver which is recorded by HDSDR and post processed with Audacity to cut and synchronize with the original. The waveforms that will be compared is thus recorded in one stereo wave file where left channel carries the demodulated signal and right channel carries original modulating signal. The results will be discussed on the chapter about Results and Discussion.

#### 6.4. VHDL CODE AND BLOCK SCHEMA OF THE SYSTEM

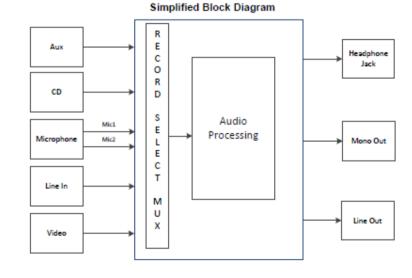

All the VHDL code of the system is given in Appendix C. As with the MATLAB codes, comments explain everything. The block schema given in Figure 6.6 summarize the functioning of the FPGA AM RX and show the relations between different modules. Top module cnt is used as a wire loom for other sub-modules and provides the interconnections between different modules of the system. Also, top module contains necessary codes to arrange clocks and resets used by sub-modules of the system.

Figure 6.6. Block schema of the FPGA AM RX system.

All the basic AM receiver functions is contained in the AM\_RX module. As seen on Figure 6.6, AM\_RX module can handle complex signals. Despite the output is also two channels, it is not in complex form. The resulting demodulated signal can only be in real format thus it is copied on both channels. The outputs of different sub-modules in AM\_RX module can be directed to the output and since many of them provides complex output when they are selected, the output of the AM\_RX module is operated in complex mode. The selection is achieved by built-in switches of the Mimas FPGA board. Also, every sub-module in the signal chain of AM\_RX module has its own clipping indicators and outputs of these indicators are directed to built-in LEDs on the board.

Complex input to AM\_RX module is firstly frequency shifted by an amount controlled by the first NCO, whose frequency control input (phase increment input) is driven by the frecalc module which in turn takes commands from sercomrx module which provides frequency setting commands received from PC through a USB-to-serial cable using a suitable terminal program such as Termite or PuTTY run on the host PC. All serial data communication is handled by the sercomrx and sercomtx modules in the FPGA design. The received commands by sercomrx module are echoed through sercomtx module to host PC. The command format is f<sign><frequency> where f represents that it is a frequency changing command, sign is either + or – and frequency is a 5-digit integer number in the range 00000 – 23999 which is the absolute value of frequency in Hz. So, the frequency can only be changed in 1Hz increments (frequency resolution is 1Hz).

The complex frequency down shifting operation sets the center frequency of the received station to zero. The complex radio signal then low-pass filtered whose cutoff frequency is set to 4KHz, which is compatible with the bandwidth of the baseband modulating test signal used in the experiments. Then the signal is complex up-shifted to 12KHz using a second fixed frequency NCO and a subsequent complex multiplier IP. This last fixed upshifting operation is necessary for demodulation.

All the FIR filters, NCOs and complex and real multipliers are implemented using ready-made Xilinx IPs which shortens design time extremely and provides high performance. Every IP used is configured and setup using respective wizards whose use is very comprehensive but explained clearly in respective datasheets of every IP. So, they will not be covered here in detail.

After second frequency shift, the signal being bandlimited to  $\pm$ 4KHz at the center frequency of 12KHz is realized by an adder and then demodulated using a squaring method which uses just a single multiplier. The resulting signal must be low-pass filtered to get rid of the high frequency products generated in the non-linear squaring process. After this the original modulating signal is obtained clearly.

All three FIR filters in the design are identical in input and output sampling rates (48KSps), bit resolution (16-bits), number of coefficients (255), coefficient resolutions (16-bits) and cut-off frequency (Fc=4KHz). So, after their coefficients found using a MATLAB script, they are implemented using the FIR filter IP design wizard and the resulting module is instantiated (copied) three times.

Signal digitization and reproduction is carried over by the LM4550 based soundcard. So, signal exchange between PC and FPGA AM RX is through audio cables in analog format. For the management of the LM4550 soundcard, a VHDL module is written by the help of the respective datasheet. The management module resets, sets up and configures the LM4550 chip prior usage and then handles the data streaming between LM4550 and Spartan6 FPGA.

As said before frequency control is achieved through a USB-to-TTL serial cable and using a terminal program in the PC. The serial link cable also provides the auxiliary 5V supply that the LM4550 soundcard necessitates since Mimas FPGA board only supplies 3.3V.

According to the design utilization summary report generated in the synthesis process by Xilinx ISE webpack suite, out of 1430 slices 702 is used which corresponds to 49% utilization. Out of 32 RAMB16WER ram blocks 30 is used which corresponds to 93% utilization. And lastly, out of 16 DSP48A1 DSP blocks 15 is used which corresponds to 93% utilization. So, in the light of these information the

design is said to be RAM and DSP intensive. It is normal for a SDR design implemented in FPGA because their signal chain usually requires RAM and DSP intensive filter and multiplier operations.

#### 6.5. RTL DIAGRAMS OF THE SYSTEM

RTL diagrams are useful in showing the internals of a design in FPGA. They provide an easy and quick way of understanding the operation of the design. They are also used as an alternative tool in the debugging process of the design. Most important modules of the system are presented here to show their operation. These are top module cnt and am\_rx modules.

Figure 6.7. RTL schematic of top module cnt.

Figure 6.8. RTL schematic of am\_rx module.

#### **CHAPTER 7**

#### **RESULTS AND DISCUSSION**

The system is simulated and tested using two 10s sound recordings firstly recorded at 8KSps and then upsampled to 48KSps to cope with the modulation process. Each recording incorporates music which fill the 4KHz spectra in a normal distrubution so that test signals provide a similar result with a white noise source. The recording is used in the modulation of two AM stations put in different frequencies with the test signal A1 on fc=5KHz and A2 on fc=-15KHz in the complex signal at 48KSps. Modulation is done using a MATLAB script whose listing given on Appendix B1. This modulated complex test signal then used in the simulation of demodulation using the code listed in Appendix B3. The test signal is also used in actual real world experiments carried on FPGA AM RX system. This is achieved by playing the test signal in a continuous loop outputted to the soundcard of PC using Audacity as the player. After demodulation by the FPGA AM RX, the resulting waveform is captured by the soundcard of the PC and monitored and recorded by the HDSDR SDR program. The resulting waveforms from simulation and test are post-processed before put into analysis using a MATLAB script which is listed on Appendix B4. Post-processing incorporates normalizing and syncronization of the resulting waveform to respective input test signal, either A1 or A2. Post-processing is carried on using Audacity. The post-process result is then recorded in 2-channel stereo format in order to preserve the synchrocity. In this format the top signal (Left channel) holds the demodulated waveform and the bottom signal (Right channel) holds the original test signal. The analysis operation provides three results: way recording of difference signal between demodulation and original test signal, rms level of error signal (obtained from difference waveform using a 10s window), Signal-to-Noise Ratio (SNR) in dB calculated from the rms error and rms level of the original test signal. Demodulation waveform, original test signal waveform and difference waveform combined in a single graphic time plot for each test signals and

for each of the simulation and test are presented in Figures 7.1-4. Also the analysis results for each of the two test waveforms for each of the simulation and test is listed in Table 7.1 for comparison.

| do    | 1.0                                                   | 2.0                   | 3.0                      | 4.0              | 5.0                     | 6.0                                                                                                            | 7.0                 | 8.0           | 9.0            | 10             |

|-------|-------------------------------------------------------|-----------------------|--------------------------|------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|---------------|----------------|----------------|

| 1.0   | 1                                                     | marine the state      | di Li Li                 |                  | 111                     | and a least                                                                                                    |                     | 1 1           |                | 4.1            |

| 0.5-  | anter beither the                                     | del and a state       | Middle and the labor     | allillille and a |                         | alife high and the                                                                                             | Welling Hard Here   | UK_ Wolder W  | and the second | Aller Lin      |

| 0.0   |                                                       | Alexander and         |                          |                  |                         | where we are a strength of the strength of the strength of the strength of the strength of the strength of the |                     |               |                | In working     |

| -0.5- | A. A. I. I.                                           | an atom the           | and the flat frame       | and a la         | and have                | change and filler                                                                                              | and the fac         | the first of  |                | le contra      |

| -1.0  |                                                       |                       | n 1 1                    | 1.1              | 1 1 1                   | 1 11                                                                                                           |                     |               | 1              | 1              |

| 0.5-  | and a line have been been been been been been been be | addition              | illight and the change   | walling          | attilles and the second | للطوا ليسم المتخ الكائلان                                                                                      | Hunder and Una Hora | his manual in | durblede la.   | Wither William |