## DESIGN AND IMPLEMENTATION OF AN EDUCATIONAL FM RECEIVER WITH FPGA USING SDR TECHNIQUES

## 2022 MASTER THESIS ELECTRICAL AND ELECTRONIC ENGINEERING

# Abdalla M Mohamed ELSALHIN

Thesis Advisor Assist. Prof. Dr. Bilgehan ERKAL

#### DESIGN AND IMPLEMENTATION OF AN EDUCATIONAL FM RECEIVER WITH FPGA USING SDR TECHNIQUES

Abdalla M Mohamed ELSALHIN

Assist. Prof. Dr. Bilgehan ERKAL

T.C.

Karabuk University Institute of Graduate Programs Department of Electrical and electronic engineering Prepared as Master Thesis

> KARABUK December 2022

I certify that in my opinion the thesis submitted by Abdalla M Mohamed ELSALHIN titled "DESIGN AND IMPLEMENTATION OF AN EDUCATIONAL FM RECEIVER WITH FPGA USING SDR TECHNIQUES" remains fully adequate in scope as well as based on the quality as a thesis for the degree of Master of Science.

Assist. Prof. Dr. Bilgehan ERKAL ...... Thesis Advisor, Department of Electrical and Electronic Engineering

This thesis is accepted by the examining committee with a unanimous vote in the Department of Electrical and Electronic Engineering as a master thesis. December 19, 2022

| Examining Committee Members (Institutions)       | <u>Signature</u> |

|--------------------------------------------------|------------------|

| Chairman: Assoc. Prof. Dr. Salih GÖRGÜNOĞLU (KU) |                  |

| Member : Assoc. Prof. Dr. Hüseyin DEMIREL (KBU)  |                  |

| Member : Assist. Prof. Dr. Bilgehan ERKAL (KBU)  |                  |

The degree of Master of Science by the thesis submitted is approved by the Administrative Board of the Institute of Graduate Programs, Karabuk University.

Assoc. Prof. Dr. Müslüm KUZU ......

Director of the Institute of Graduate Programs

"I declare that all the information within this thesis has been gathered and presented in accordance with academic regulations and ethical principles and I have according to the requirements of these regulations and principles cited all those which do not originate in this work as well."

Abdalla M Mohamed ELSALHIN

#### ABSTRACT

#### M. Sc. Thesis

## DESIGN AND IMPLEMENTATION OF AN EDUCATIONAL FM RECEIVER WITH FPGA USING SDR TECHNIQUES

Abdalla M Mohamed ELSALHIN

Karabük University Graduate School of Natural and Applied Sciences Department of Electrical and Electronic Engineering

> Thesis Advisor: Assist. Prof. Dr. Bilgehan ERKAL December 2022, 94 page

The complexity of hardware in traditional FM radio lead to huge radio size, noisy, difficulties in maintenance as well as higher production costs. In addition to limitation on protocols in addition, which is associated with frequency bands supported, which lead to utilize diverse radio devices for diverse networks also communication protocols. Software Defined Radio techy provides an efficient in addition, which is associated with comparatively inexpensive solution to these problems replacing a lot of cascaded electronics components via a single digital chip FPGA (Field Programmable Gate Array) resulting in low production cost, immunity to noise, ease of maintenance as well as enormous reduction of radio size. In this paper, digital FM receiver was designed in SIMULINK in addition, which is associated with test results. Simulation results in addition, which is associated with test results. Simulation results

come from ideal simulation studies under MATLAB environment utilizing the codes listed on Appendix A.

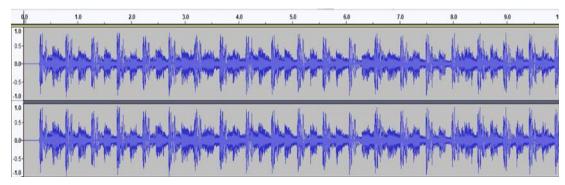

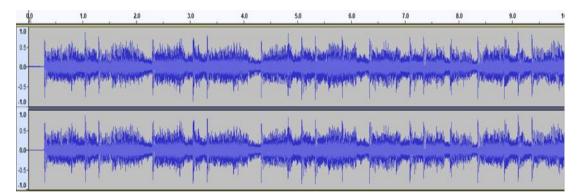

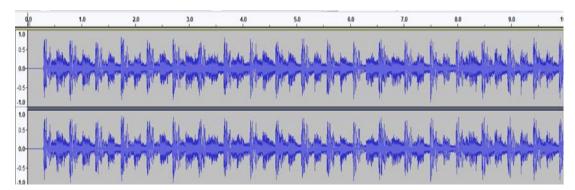

Test results come from as recordings from real world tests of FMRX frameworks implemented on FPGA. Two frequency modulated test signals utilized in each stage are FM1 as well as FM2 which are derived utilizing two test recordings A1 also A2 respectively as the modulating signal. Each test signal lasts 10 seconds as well as sampled at a rate 48KSps. Results from simulation as well as tests, which are demodulated audio, are recorded as a separate wave file

**Key Words** : Sdr, Fpga, Vhdl, Matlab, Fm. **Science Code** : 90523

#### ÖZET

#### Yüksek Lisans Tezi

## EGITIM AMAÇLI SDR TEKNIKLERINE DAYALI FPGA TABANLI FREKANS MODÜLELI RADYO ALICISI TASARIMI VE UYGULAMASI

#### Abdullah M Muhammed ELSALIHIN

Karabük Üniversitesi Lisansüstü Eğitim Enstitüsü Elektrik-Elektronik Mühendisliği Anabilim Dalı

> Tez Danışmanı: Dr. Öğr. Üyesi Bilgehan ERKAL Aralık 2022, 94 sayfa

Geleneksel (FM) radyoda donanıma dayalı karmaşıklığın ana noktası, daha büyük radyo boyutları, gürültü, bakım zorlukları gibi bazı noktalara yönlendirilmiş ve buna ek olarak daha yüksek üretim maliyetleri ile ilişkilendirilmiştir. Ayrıca, frekans bantlarına bağlanan desteklenen protokollerdeki sınırlamalar, iletişim protokollerinin yanı sıra farklı ağlar için farklı radyo cihazlarının kullanılmasını zorunlu kılmaktadır. Aynı şekilde, Yazılım Tanımlanabilir Radyo teknolojisine, örneğin, Programlanabilir Kapı Dizisi Alanına dayalı tek bir dijital çip ((FPGA) ile birden fazla kademeli elektronik bileşenin değiştirilmesi gibi kaydedilen bu sorunlara karşı etkili ve nispeten ucuz bir çözüm sunulmuştur. Düşük üretim maliyeti, gürültü bağışıklığı, radyoya bağlı bakım kolaylığı ile bağlantılı Alan Programlanabilir Kapı Dizisi) boyutunda muazzam bir azalma sağlar. Bu çalışmada sayısal (FM) alıcı (MATLAB) kullanılarak tasarlanmış ve üzerinde başarıyla uygulanmıştır. Ayrıca, çalışmanın iki ana aşamada elde edilen bazı gerekli sonuçları vardır: simülasyon sonuçları ve test sonuçları. Ayrıca simülasyon sonuçları (MATLAB) ortamında bazı önemli kodları kullanarak simülasyon çalışmalarının idealinden gelmektedir. Bu nedenle, test sonuçları, (FPGA) üzerinde uygulanan (FMRX) çerçevesine dayalı gerçek dünya testlerinden kayıtlar olarak gelir. Her adımda, modülasyon sinyalleri olarak sırasıyla A1 ve A2 test kayıtları kullanılarak türetilen (FM1) ve (FM2) olan iki frekans modülasyonlu test sinyali kullanılmıştır. Ek olarak, her test sinyali on saniye sürer ve (48KSps)'de örneklenir. Ek olarak, demodüle edilmiş sesle bazı gerekli testler ile desteklenen simülasyonların sonuçları ayrı bir wave dosyası olarak kayıtlı kalır. Sonuç olarak, bu kazanımlar birbirleriyle karşılaştırılarak iyi sonuçlar elde edilmiştir. Ayrıca sonuçlar, (FMRX) çerçevesinin iletişim mühendisliği öğrencilerine dayalı çok yönlü bir eğitim ortamı olduğunu kanıtlamaktadır.

Anahtar Kelimeler: Sdr, Fpga, Vhdl, Matlab, Fm.Bilim Kodu: 90523

### ACKNOWLEDGMENT

I would like to give thanks to my advisor, Assist. Prof. Dr. Bilgehan ERKAL, for his great interest and assistance in preparation of this thesis.

## CONTENTS

| APPROVALii                                                  |

|-------------------------------------------------------------|

| ABSTRACTiv                                                  |

| ÖZETvi                                                      |

| ACKNOWLEDGMENTviii                                          |

| CONTENTSix                                                  |

| LIST OF FIGURESxiii                                         |

| LIST OF TABLESxiv                                           |

| SYMBOLS AS WELL AS ABBREVITIONS INDEXxv                     |

| CHAPTER 1                                                   |

| INTRODUCTION                                                |

| 1.1. LITERATURE REVIEW                                      |

| CHAPTER 2                                                   |

| SOFTWARE DEFINED RADIO (SDR)                                |

| 2.1. SDR BASED ON SOME AADVANTAGES                          |

| 2.2. SDR AS WELL AS DISADVANTAGES                           |

| 2.3. IDEAL BASED ON THE SDR DESIGN                          |

| 2.4. THE RESEARCH MOTIVATION                                |

| 2.5. THE SDR AS A HARDWARE                                  |

| 2.5.1. The Traditional Main Receiver                        |

| 2.6. THE SDR AS A RECEIVER 10                               |

| 2.7. SDR TRANSMITTER                                        |

| CHAPTER 3                                                   |

| THE MAIN FIELD BASED ON THE PROGRAMMABLE GATE ARRAYS (FPGA) |

| 3.1. FPGA ARCHITECTURE                                      |

| 3.1.1. Logic Cells                                          |

| ix                                                          |

| CHAPTER 4                                                                 | .17  |

|---------------------------------------------------------------------------|------|

| FREQUENCY MODULATION (FM)                                                 |      |

| 4.1. FM MODULATION AND DEMODULATION                                       |      |

| 4.1.1. Frequency Modulation                                               |      |

| 4.1.2. Frequency Demodulation                                             |      |

| 4.2. FREQUENCY MODULATION ADVANTAGES AS WELL AS                           |      |

| DISADVANTAGES                                                             |      |

| 4.2.1. Advantages Based on the Frequency Modulation, FM                   |      |

| 4.2.2. Disadvantages Based on the Frequency Modulation, FM                |      |

| 4.3. MODULATION INDEX AS WELL AS DEVIATION RATIO                          |      |

| 4.3.1. Sinusoidal Baseband Signal                                         |      |

| 4.3.2. Modulation Index                                                   | . 22 |

| 4.4. FM BANDWIDTH                                                         | . 22 |

| 4.5. CARSON'S RULE BASED ON THE FM BANDWIDTH                              | . 23 |

| 4.6. FREQUENCY MODULATION EQUATIONS                                       | . 24 |

| 4.7. FM DEMODULATOR                                                       | . 24 |

| 4.8. NOISE REDUCTION                                                      | . 25 |

| 4.9. QUAD RATURE FM DEMODULATOR                                           | . 25 |

| 4.10. FM QUAD RATURE DEMODULATOR BASICS                                   | . 26 |

| 4.11. QUADRATURE DETECTOR ADVANTAGES & DISADVANTAGES                      | . 27 |

| CHAPTER 5                                                                 | 28   |

|                                                                           |      |

| VHDL –HARDWTHAT ARE DESCRIPTION OF THE USED LANGUAGE                      |      |

| 5.1. VHDL BASED ON SEVERAL CONCEPTS                                       |      |

| 5.1.1. Behavioural based on Modelling                                     |      |

| 5.1.2. The Main Structural Modelling                                      |      |

| 5.1.3. RTL based on the Register Transfer Level based on several Diagrams |      |

| 5.2. VHDL DESIGN STAGES                                                   |      |

| 5.2.1. Entity                                                             |      |

| 5.2.2. Architecture                                                       | . 31 |

| 5.2.3. The Main Package                                                   | . 31 |

| 5.2.4. Process                                                            | . 31 |

| 5.3. VHDL MODELLING BASICS                                                | . 32 |

| 5.3.1. Constants                                                          | . 32 |

|                                                 | <b>Page</b> |

|-------------------------------------------------|-------------|

| 5.3.2. The main associated Signals              |             |

| 5.3.3. VHDL Operators                           |             |

| 5.3.4. Concurrent Based on a Signal Assignments |             |

| CHAPTER 6                                  |

|--------------------------------------------|

| IMPLEMENTATION OF FM RECEIVER IN FPGA      |

| 6.1. HARDWARE DEVELOPMENT                  |

| 6.1.1. FPGA Board Spartan CX7A35T          |

| 6.1.1.1. Introduction                      |

| 6.1.1.2. Board Based on Some Features      |

| 6.1.2. Analog to Digital Signal Converter  |

| 6.1.2.1. Introduction                      |

| 6.1.2.2. Board Features                    |

| 6.1.3. Digital to Analogy Signal Converter |

| 6.1.3.1. Introduction                      |

| 6.1.3.2. Board Features                    |

| 6.2. PROGRAMS                              |

| 6.2.1. Matlab                              |

| 6.2.2. HDSDR                               |

| 6.2.3. The Audacity                        |

| 6.3. SIMULATION STUDIES                    |

| 6.4. SOFTWARE DEVELOPMENT                  |

|                                            |

| CHAPTER 7                                  |

| RESULTS AND DISCUSSION                     |

|                                            |

| CHAPTER 8                                  |

| CONCLUSION                                 |

|                                            |

| REFERENCES                                 |

|                                            |

|                                            |

|                                                        | <u>Page</u> |

|--------------------------------------------------------|-------------|

| APPENDIX C. DATASHEETS OF CHIPS UTLIZED IN THE PROJECT | 90          |

| RESUME                                                 | 94          |

## LIST OF FIGURES

| Figure 2.1. The Functional main block diagram based on the wireless as well as communication framework         |

|----------------------------------------------------------------------------------------------------------------|

| Figure 2.2. Internal actual blocks based on the super heterodyne of the receiver9                              |

| Figure 2.3. The main Block Diagram based on the SDR AS a Receiver                                              |

| Figure 2.4. The block Diagram based on the SDR Transmitter                                                     |

| Figure 3.1. Internal of a Structure based on the (FPGA)                                                        |

| Figure 3.2. The main basic of (FPGA) the main Architecture                                                     |

| Figure 3.3. The main contemporary based on (FPGA) which associated with the Architecture. 15                   |

| Figure 3.4. The Logic based on a Cells                                                                         |

| Figure 4.1. Frequency Modulation                                                                               |

| Figure 4.2. Block Diagram of Digital FM Receiver Circuit                                                       |

| Figure 4.3. Demodulator for quadrature FM in                                                                   |

| Figure 6.1. The main general representations based on the FPGA (FM) Receiver 34 $$                             |

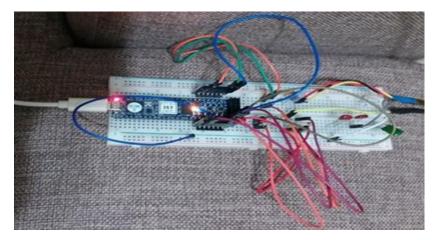

| Figure 6.2. Photo of the frameworks in Operation                                                               |

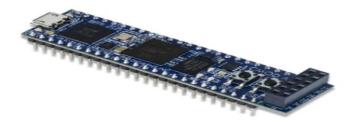

| Figure 6.3. FPGA developed BOARD SPARTAN CMODA7-35T                                                            |

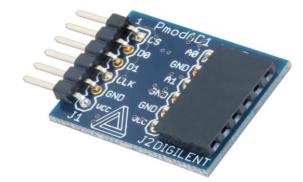

| Figure 6.4. The Analog to Digital Signal Converter                                                             |

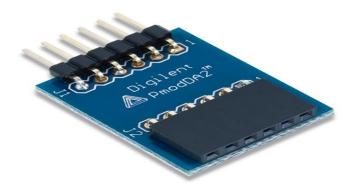

| Figure 6.5. Digital to Analogy Signal Converter                                                                |

| Figure 6.6. Audacity audio processing software                                                                 |

| Figure 6.7. HDSDR SDR software                                                                                 |

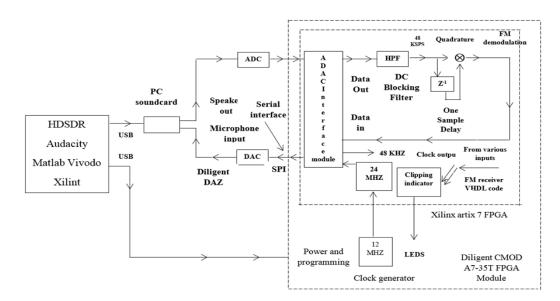

| Figure 6.8. The main associated basic block as a diagram of the FMRX frameworks implemented in the FPGA fabric |

| Figure 7.1. Simulation result for A1                                                                           |

| Figure 7.2. Simulation result for A2                                                                           |

| Figure 7.3. Test result for A1                                                                                 |

| Figure 7.4. Test result for A2                                                                                 |

## LIST OF TABLES

| Table 7.1. SNR in addition, | which is associated with the rms error for each |   |

|-----------------------------|-------------------------------------------------|---|

| simulation as we            | 11 as test                                      | 0 |

## SYMBOLS AS WELL AS ABBREVITIONS INDEX

### ABBREVITIONS

| FM    | :Frequency Modulation                               |

|-------|-----------------------------------------------------|

| AM    | :Amplitude based on Modulation                      |

| SDR   | :Software as a Defined Radio                        |

| DSP   | :Digital Signal Processors                          |

| FPGA  | :Field Programmable regarding to a Gate Arrays      |

| RF    | :Radio Frequency                                    |

| IF    | :Intermediate Frequency                             |

| SNR   | Signal-to-Noise Ratio                               |

| PSK   | Phase Shift Keying                                  |

| DAC   | :Digital-towards-Analog Converter                   |

| PLL   | :Phased Locked Loop                                 |

| ADC   | :Analog towards a Digital Converter                 |

| ASIC  | :Application based on a Specific Integrated Circuit |

| DDC   | :Digital Down Converter                             |

| HDL   | :Hardware Description Language                      |

| LUT   | :Look Up Table                                      |

| RAM   | :Random Access Memory                               |

| VHSIC | :Very High Speed Integrated Circuit                 |

| VHDL  | :VHSIC Hardware Description Language                |

| PCB   | :printed circuit board                              |

| FF    | :Flip-Flop                                          |

| IC    | :integrated circuit                                 |

| PLD   | :programmable logic device                          |

| CLB   | :configurable logic blocks                          |

| RTL   | :Register Transfer-Level                            |

#### **CHAPTER 1**

#### **INTRODUCTION**

Wireless communication channels have become more commonplace since the advent of cellular communication in the past twenty years. Right now, hardware flexibility is necessary for the development of wireless applications as well as wireless techy. Making a new based on radios in response towards the evolution of wireless applications which is associated with the standards is time-consuming as well as extremely expensive [1]. Therefore, software based on the radio can address these issues via converting analog components to digital components. Programmable logic devices, for instance, Field Programmable Gate Arrays, can be utilized to implement radio functions (FPGAs).

Consequently, it was frequently challenging to update as well as modify these frameworks. Several of the encoders, modulators as well as filters, in addition, which is associated with decoders needed via some sorts based on the communication frameworks can now be implemented in software for the reason that to advancements in digital signal processor (DSP) techy [2].

While some frameworks implement all of their baseband functions in software, others just utilize it for minor tasks. Software defined radios (SDRs) are frameworks that the implementation based on all of their baseband functionality in software [3].

SDR are evolving into a preferable substitute for conventional radio frameworks thanks largely to their adaptability. Reprogramming SDRs makes them somewhat upgradeable for the reason that they have this capability. Though the term "future-proof" may be utilized too strongly, the idea is nonetheless well-made.

SDRs can accommodate a huge variety of waveforms as well as coding schemes, which makes them an extremely appealing alternative to traditional frameworks when waveforms evolve in addition, which is associated with require expensive replacement. In some circumstances, SDRs can take the place of a number of conventional radios [4].

Compared to, say, AM, the FM app has a higher signal-to-noise ratio (SNR). For audio communication channels, it is permitted to prepare from 5 towards 15 dB as compared to AM optimization the scheme. More improvement can be achieved via utilizing FM Wider deflection. For signal-to-noise (SNR) improvement in FM frequencies, additional methods, for instance, pre-emphasis on loudness Frequencies with the corresponding focus in the receiver, are typically applied. FM receivers typically incorporate selections that exclude AM noise for the reason that FM signals have a set amplitude, greatly enhancing SNR. [5] [6].

#### **1.1. LITERATURE REVIEW**

Since the discovery of the first wireless communication in the late 1980s, many advancements in radio communication techy have been made with the goal of ensuring that radio utilizers are always connected. Attributable to bandwidth restrictions at the time, triumphant radio, the first sort of broadcast, employed analog voice communication. In the 1950s, broadcast communication took over, in addition, which is associated with analog television transmission became the norm. This type of communication utilized a lot of bandwidth but provided exceptional customer service. The usage of computers, which could send data over great distances which is associated with make utilize of both wired in addition, which is associated with wireless connections, gained popularity in the 1960s. After the development of cell phones, wireless voice communication was later discovered, enabling transmission from any location. However, the mobile devices were difficult to utilize for the reason that they were not portable [4].

Ahmeda Gareane talked about utilizing the Softrock Ensemble RXTX SDR transceiver for FM signal transmission as well as receiving. Two input frequencies

also a modulation index were utilized as inputs for the developed frameworks to generate in addition, which is associated with plot FM signals utilizing MATLAB. The FM modulation as well as FM demodulation stages of the frameworks were both present. To convey a recorded audio file, the carrier signal frequency was modified during the FM modulation stage dependent on the signal strength. The resulting modulated wave is then transferred to the receiver. A low pass filter was utilized in the FM demodulation stage to recover the audio signal from the modulated wave, removing the carrier frequency in addition, which is associated with allowing the audio signal to be transmitted to the speaker. Then, Audacity was utilized to examine in addition, which is associated with listen to the signal. Modulation as well as demodulation were performed utilizing Matlab software methods [7].

Ali Hander created an AM receiver in addition, which is associated with utilized SDR techniques to put it in an FPGA. His study's major goal was to develop a low-cost, straightforward FPGA-based platform for teaching SDR fundamentals. First, MATLAB scripts were utilized to create a simulation environment for the investigation. MATLAB scripts were utilized to generate an AM test signal from a collection of test signals. The signal was utilized in the testing as well as simulation of Implementation of FPGA. A foundation for that (VHDL) design based on the FPGAbased SDR framework which is also provided via simulation code. To compare in addition, which is associated with contrast the test also simulation findings, another MATLAB script was built. The results of those tests on the two signals showed that, since the greater SNR ratio is better, based on some sorts of some main tests which is associated with the signal A1 remain superior than the main tests by means of a signal A2. It has been found that the sort based on a real-world (SNR) findings remained marginally lower than the value of the main value of the simulations based on the (SNR) when has been compared with the main actual real-world values which is associated with the simulations for each test signal. SNR levels greater than the value 20dB, which were considered acceptable for an AM receiver, remained found in test results. Whereas test as well as simulation findings demonstrated that an effective candidate for AM demodulation in addition, which is associated with reception is an FPGA AM RX frameworks. The developed and implemented FPGA AM RX

framework remained which is associated with helpful in teaching fundamental SDR principles, which served as the study's major focus [8].

In the Caner KREMTC investigation, Matlab codes were utilized to model the modeling of the main amplitude modulated based on the radio transmitter in (FPGA). The amplitude modulated transmitter remained then that has been implemented on the (FPGA) board after the VHDL code remained generated on (ISE) Design Suite (14.7). (Mimas Spartan 6). The Audacity program sends a sample sound recording towards the (FPGA) card via the sound card in order towards modulating it. ADC (LM4550) card sent an analog signal towards the FPGA card, which then demodulated in addition, which is associated with the recorded the transmitter signal utilizing the HDSDR application.

The DAC (LM4550) card on the FPGA card converted the analog transmitter signal into analog form, which it then passed towards the laptops based on the sound card's microphone input. Finally, utilizing Matlab code, the captured transmitter signal was offline demodulated, in addition, which is associated with the the output was saved to the hard drive. The data analysis revealed that, for the identical test signal, there was very little variance amongst the simulation findings as well as the actual test results. Given that the signal was subjected to outside noise during actual tests, this was thought to be a totally plausible circumstance. A similar average value of about 20 dB was seen when the acquired SNR values were evaluated; this value was suitable for AM modulation. It was determined that the (FPGA) based on the AM transmitter frameworks could successfully realize AM broadcasts. The Ali HANDER architecture has produced a solid foundation for the deployment in addition, which is associated with the training of SDR frameworks on FPGA [9].

The design process in addition, which is associated with the implementation outcomes of a software defined radio (SDR) employing an Altera Cyclone II family board were provided via Hikmat N. Abdullah. The Cyclone II development in addition, which is associated with the educational board, Embedded Matlab blocks, as well as Matlab/Simulink were utilized in the implementation. The Matlab/Simulink platform was utilized to implement the idea initially. The Simulink HDL coder was then utilized to convert it to VHDL level. The Quartus II 9.0 Web Edition® software was utilized to synthesize the design before it was downloaded to an Altera Cyclone II board. The findings demonstrated that employing programmable logic tools, SDR implementation is simple to create in addition, which is associated with the comprehend. A useful design flow of the process utilized to obtain VHDL netlists that can be downloaded to FPGA boards was also provided via Hikmat N. Abdullah [10].

#### **CHAPTER 2**

#### SOFTWARE DEFINED RADIO (SDR)

SDR has gained popularity as an alternative to conventional radio frameworks mostly for the reason that of its flexibility. The potential for SDR has been reprogrammed, so it can be upgraded towards some extent. Although proving the future might be a fairly bold statement, the idea is well made. A huge variety of waveforms as well as encoder charts are supported via SDR. This is a particularly appealing choice for the reason that conventional frameworks need to be replaced on a costly basis as techy develops in addition, which is associated with the waveforms change. SDRs might only need a small upgrade. SDRs can occasionally take the place of a large number of conventional radios [11]. The expense of the job task is lower as well as the radios are simple to utilize. There are various ways to enumerate what Software Defined Radio (SDR) is. A radio remains a wireless device that sends which is associated with receives frequencies as well as information. In order to access the SDR, a number of issues must be overcome, including modifying the frameworks specifications in accordance with the several applications we may return, including modification, extraction, in addition, which is associated with the encryption. As a conclusion, this information aids in the reception of these criteria [12].

#### 2.1. SDR BASED ON SOME AADVANTAGES

- Point as well as Click Control

- Easy based on the Tuning

- A PC Is based on the Sharing of the Workload

- Cheaper for several situations

- Is Smaller

- Visual based on the look at a signal

- Open CV Platforms

• Custom based on the Filtering Utilizes modern techy

#### 2.2. SDR AS WELL AS DISADVANTAGES

- Filtering based on the Traded for Space

- Hard towards run on old computers

- Sending remains more expensive

- The framework remains dependent on PC

- Software based on some Limits

#### 2.3. IDEAL BASED ON THE SDR DESIGN

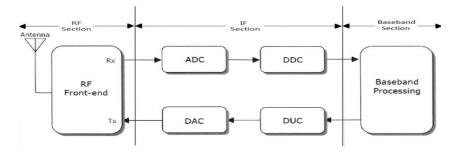

One of the most important modern technologies for aiding the main communication based on in military service insecurity, war, in addition, which is associated with the peace is the software-defined radio frameworks (SDR). Instead of utilizing a traditional radio, SDR converts wireless signals at the best radio frequencies to an analog IF that can be utilized with regular radios. The conversion of an analog based on the signal towards a digital value of frequency (ADC) in an IF as well as the signal's conversion from a digital to an analog FM frequency (DAC) in an IF are both depicted in Figure 2.1. The handling of hardware in the receiver in addition, which is associated with the transfer based on the signal routed via the main converter sampling rate via the interface (ADC). SDR may process baseband utilizing a variety of digital devices, including as field-programmable gate arrays as well as digital signal processors (DSP) as well as (the main value FPGA).

Figure 2.1. The Functional main block diagram based on the wireless as well as communication framework.

A Digital devices include benefits including reduced energy use, fast processors, in addition, which is associated with the flexibility. However, there is a contrast amongst the extreme degrees of flexibility as well as the rise in energy consumption for DSP to minimally limit the flexibility in addition, which is associated with the lower energy consumption than ASICs. FPGA offers more flexible, less expensive in addition, which is associated with the energy-efficient devices than DSP as well as ASICs. FPGA in addition, which is associated with the redesign have improved SDR performance [13].

#### 2.4. THE RESEARCH MOTIVATION

SDR is mainly Looks like as a several techies in terms of development, goes via the name Speakeasy, in addition, which is associated with the has both military as well as non-military uses. Amongst (1991) as well as (1995), the United States' naval forces employed it. The fundamental laws, knowledge, radio program, wireless communication, in addition, which is associated with the programming were all greatly improved via this techy. Currently, all SDR software is inexpensive towards purchasing. [14].

#### 2.5. THE SDR AS A HARDWARE

#### 2.5.1. The Traditional Main Receiver

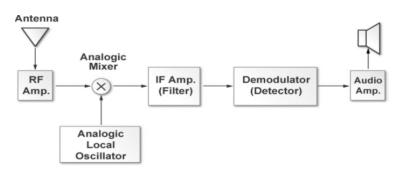

Towards determining the main associated sign in the main associated carrier frequency based on the setting of frequency of shifting, in addition, the candidate remains filtering as well as isolated from others utilizing the conventional receiver, the traditional demodulation, in addition, which is associated with the three processes. Enlargement via mass demodulation is utilized to insert compensation for enlargement-related transport losses. The majority of traditional receiving setups have been utilizing various strategies for about a century since they must transport the signal to the required level for circuit demodulation. Figure 2.2 illustrates how the fundamental design helps to distinguish amongest the conventional in addition, which is associated with modern reception SDR methods.

Figure 2.2. Internal actual blocks based on the super heterodyne of the receiver.

Based on the Figure. 2.2. Has represents that how the antenna based on the main interferes with signals. A transferring the main associated reference towards the mixer during the other input, which gets the contribution oscillator decoration in addition, which is associated with the designating local frequency oscillator, is the signal amplified during the duration of RF phase, which operates in the frequency range of benefit. The mixer is in charge of changing the frequency to the medium frequency via adjusting the radio, which translates the frequency signal mediator (IF) which is IF.

The main purpose based on the appointing a frequency oscillator is utilized to verify if the frequency signal's timing variance is equal to (IF). For instance, if the IF was supposed to be at 10.7 (MH)z in addition, which is associated with the the FM station's frequency remains 100.7 (MHz), the oscillator which has been required to be set to 90 MHz as an outcome of the low side of the main point of transformation. Therefore, the next phase based on the involvement of weakening all candidate wave signals, though undoubtedly a portion of the spectrum. The bandwidth prevents the band's received signal from being visible. If it only utilizes one substitution, the demodulator restores the original signal changed at the conclusion of the stage through the speakers. It depends on the main goal purpose via which it's intended towards boosting the signal processing recipient device. In addition, based on the cross of INFO learned towards a loudspeaker connected towards the speaker [15, 16].

#### 2.6. THE SDR AS A RECEIVER

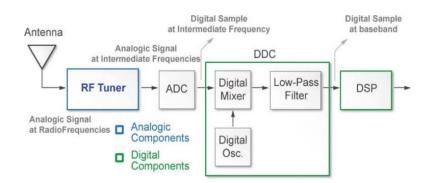

Figure 2.3. The main Block Diagram based on the SDR AS a Receiver.

Based on the Figure. 2.3 to take in the SDR signal in addition, which is associated with be the first to pass it the first three boxes of the alternative reception device are where the procedure is carried out via the RF tuner, which converts the analog signal to IF to be identical. Frameworks [17].

At that moment, a cross-reference IF the frequency band is altered via the ADC, the following phase in addition, which is associated with the digital converter are fed new data. DDC is an important component of the SDR frameworks; it is inexpensive as well as has three basic components. Follows:

- The digital based on the local oscillator.

- The digital based on the mixer.

- The main Finite of pulsation based on the response (FIR) based on the low-scrolling IF filter.

Reference based on the transfers from the counter of phase elements via the analysis [18] towards the matching baseband in our digital mixer. Furthermore, the reference remains needed far away which is associated with up to 0Hz, in addition, which is associated with the variance with the bandwidth together with being a low-pass filter as well as detecting any receiver portion is a suitable signal. This is a modified digital local oscillator. Another strategy involves lowering the sampling frequency or the sampling ratio in order to create new samples from the baseband via splitting the original sample's frequency utilizing an N element. The decimation element is what it

has been called. Via Nyquist, based on the main ratio of the final sample may be less than twice the higher-frequency components theory. The eventually, samples moving to baseband digital signal processing in a DSP box, for instance, decoding as well as demodulating [19].

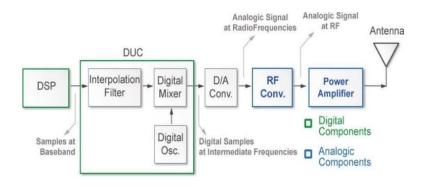

#### 2.7. SDR TRANSMITTER

As shown in In Figure. 2.4, the baseband of signal that the SDR will transmit is produced via the DSP. The first box, known as a DUC (Digital User Converter), converts the baseband signal into an IF signal via adjusting its pass band.

When (RF) remains moving based on towards the main high-frequency value of signal, the DAC sends the main associated samples towards the field analog. The signal is then enlarged as well as sent from the main associated main antenna. DUC Filter is in charge of the baseband signal's high sample ratio, which is necessary for the elements to operate properly in addition, which is associated with the causes the reverse process towards occurring at the main associated reception based on a frequency [18, 19].

Figure 2.4. The block Diagram based on the SDR Transmitter.

#### **CHAPTER 3**

# THE MAIN FIELD BASED ON THE PROGRAMMABLE GATE ARRAYS (FPGA)

The (FPGA) by means of a device with reconfigurable gate array logic circuits in a matrix. The internal circuitry of an FPGA is coupled in such a way during construction that in addition, the main associated hardware implementation based on the software application outcomes. FPGAs employ specialized hardware to process logic rather than an operating frameworks. Since FPGAs are parallel devices, various activities do not compete for the same resources. Consequently, one aspect of the application's performance changes when more processing is added is not influenced.

Additionally, several control of some loops can run at various ratios on a single FPGA chip. The operator-mandated I/O can be blocked via the main critical interlock based on the logic, which can be imposed via FPGA-based control frameworks. However, unlike hard-wired printed circuit board designs that have reliable hardware resources, FPGA-based frameworks have the potential to rearrange their internal circuitry to aid in reconfiguration when the control framework is deployed in the field.

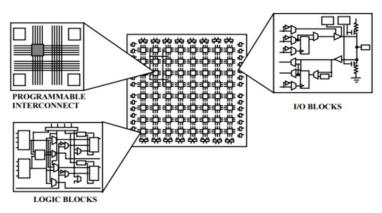

FPGA provides the specialized hardware circuitry with dependability in addition, which is associated with the performance. Through the usage of FPGA, millions of logic gates can be combined into the main associated single based on an integrated circuit (IC) chip to replace thousands of discrete elements. The main internal based on several resources of the FPGA chip include a matrix of reconfigurable logic blocks surrounded via a peripheral of I/O blocks, as depicted in Figure 3.1.below. The several signals remain routed inside the FPGA matrix utilizing wire routes as well as programmable connections switches.

Figure 3.1. Internal of a Structure based on the (FPGA).

#### **3.1. FPGA ARCHITECTURE**

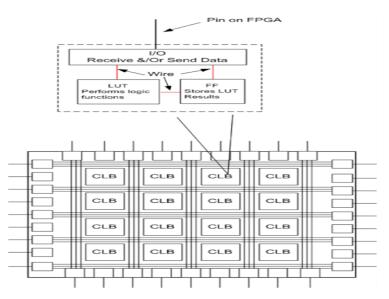

The FPGA structure is made up of various parts, including:

- The look-up table (LUT) is a component that performs a variety of logical operations.

- Flip-Flop (FF): The LUT result is stored in this register component.

- Wires: These parts link other parts together.

- Input as well as an output ((I) as well as (O)) pads: These physical ports remain utilized towards transfering data into in addition, which is associated with the out of the FPGA.

The collection of these parts combine to provide the fundamental framework of an FPGA, as shown in Figure 3.2. Although this structure is effective at implementing any algorithm, the finished implementation's proficiency remains limited based on some terms of computed output as well as realistic clock frequency, in addition, which is associated with the required resources.

Figure 3.2. The main basic of (FPGA) the main Architecture.

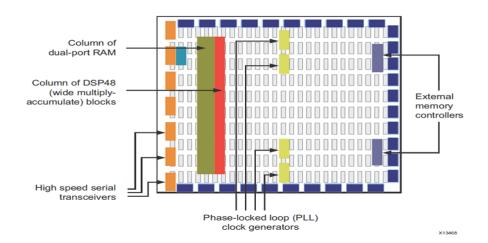

The main modern FPGA design consists of a number of fundamental building blocks that are joined via additional computational in addition, which is associated with storage units to improve the efficiency in addition, which is associated with the computational density of the hardware. The following parts will address the other elements that remain as follows: follows:

- Embedded memory towards keeping the dispersed info.

- Phase-locked several loops (PLLs) for various clock ratios to drive the FPGA fabric.

- Devices for serial transmission in addition, which is associated with the reception at high speeds.

- Memory controller's off-chip

The combination of these elements enables the FPGA to implement any software algorithm based on some running on processors, creating the contemporary FPGA architecture displayed in the Figure. 3.3. Below.

Figure 3.3. The main contemporary based on (FPGA) which associated with the Architecture.

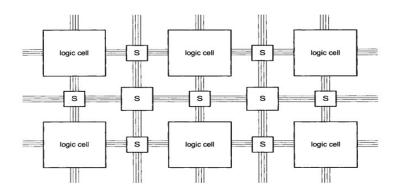

#### 3.1.1. Logic Cells

The simple each logical cell in an FPGA can be set towards performing as a wide range of operations. There is a fixed number of entries in addition, which is associated with the exits for each logic cell. The type of logic towards cells found in FPGAs is follows:

- Multiplexer logical based cells, for instance, Actel (FPGAs)

- Cells with memory-based logic, for instance, Xilinx (FPGAs)

A very broad view of the fundamental internal structure of an FPGA is presented. in the main Figure. Of the .3.4.below.

Figure 3.4. The Logic based on a Cells.

As presented in Figure. 3.4. a programmable connectivity in addition, which is associated with the adjustable logic make up the internal structure of an (FPGA) cells.

#### **CHAPTER 4**

#### **FREQUENCY MODULATION (FM)**

#### 4.1. FM MODULATION AND DEMODULATION

#### 4.1.1. Frequency Modulation

Frequency modulation refers to the process where via the carrier surge frequency is altered to match the signal density (FM) [20].

When a signal is modulated with frequency, only the carrier surge's frequency is altered to match the signal the carrier surge amplitude, or the amplitude of the modulated surge residue [21].

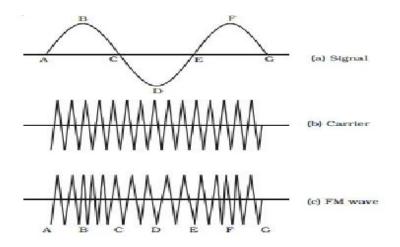

The immediate amplitude based on the main associated signal, as depicted in Fig. 1, determines how the frequency divergence of the transporter surge counts. The carrier frequency is 0 when the signal voltage is zero, as it is for A, C, E, as well as G is unchanged. The careful diverge period demonstrates that the transporter frequency is too excessive when the signal approaches its positive summit, as at B also F. However, as evidenced via the most spaced period [22], the carrier frequency is small to minimum due to the negative peak of the signal as at D.

Figure 4.1. Frequency Modulation.

#### 4.1.2. Frequency Demodulation

To correctly demodulate a modulation as well as restore the original signal, as with any modulation, is essential. The FM demodulator is also known as an FM detector, an FM discriminator, or any other number of names.

The frequency fluctuations of the entering signal can be transformed into amplitude variations on the output via a variety of diverse FM demodulators, all of which are capable of doing so. If data is being transmitted across the framework, these are typically fed into a digital interface or an audio amplifier.

In terms of practical application, frequency modulation (FM) is comparable to a straightforward balance where the baseband data signal's data or message signal changes the transporter wave's recurrence. Sound transmissions that are transmitted through FM radio channels are the most well-known FM signals. On the other hand, the FM can also communicate Radio Broadcast Data frameworks (RBDSs), which are sophisticated computerized data with modest transmission speeds. [23].

# 4.2. FREQUENCY MODULATION ADVANTAGES AS WELL AS DISADVANTAGES

There are a number of benefits also drawbacks to utilizing this type of modulation, as with any other. Before making any option or judgment regarding its utilize, they must be taken into account:

#### 4.2.1. Advantages Based on the Frequency Modulation, FM

Frequency modulation has become widely used in a range of applications, including two-way radio communications as well as high-quality audio transmission, as a result of its many advantages. Resilience to noise: resistance to noise is one of its main benefits.

Frequency modulation has the robustness to changes in signal strength as a distinct advantage. Only frequency fluctuations are used to convey the modulation. This means that as long as the signal does not decrease to a level where the receiver cannot handle it, any changes in signal level won't have an impact on the audio output. For the reason that of this, FM is perfect for mobile radio communication uses like more broad twoway radio communication or portable uses where signal levels are expected to vary greatly. The resistance of FM to interference in addition, which is associated with noise is another benefit. For the reason that of this, FM is utilized to transmit high-quality broadcast signals.

Modulation is simple to implement at the transmitter's low power stage: The transmitters are connected to another benefit of frequency modulation. It is possible to apply the modulation to a low power stage of the transmitter, which is associated with a linear type of amplification is not required to enhance the ratio of the signal's initial power to its ultimate value.

Frequency modulated signals can be amplified effectively utilizing RF devices: In a transmitter, FM signals can be amplified utilizing non-linear RF amplifiers, which are more effective than the linear ones needed for signals with any amplitude changes, for

instance, AM as well as SSB. The use of FM is thus more practical for portable twoway radio applications for the reason that less battery power is needed for a given power output.

#### 4.2.2. Disadvantages Based on the Frequency Modulation, FM

The drawbacks of frequency modulation, like those of all other frameworks as well as methods, must be taken into account before deciding whether to utilize FM.

FM has a lower spectral efficiency than several other modulation formats: In some cases, frequency shift keying, a type of frequency modulation, is less effective at transmitting data than quadrature amplitude modulation in addition, which is associated with other phase modulation forms. So, the majority of data transmission framework utilize PSK as well as QAM.

Requires more complicated demodulator: One of the minor drawbacks of frequency modulation is that the demodulator is a little more complicated as well as hence a little more expensive than the extremely simple diode detectors used for AM. Due to the prevalence of radio integrated circuits with built-in frequency demodulators, this is a much less pressing concern today.

Around other modes have higher data spectral efficiency: In comparison to frequency shift keying, a type of frequency modulation, some quadrature amplitude modulation in addition, which is associated with phase modulation formats are more spectrally efficient for data transmission. As a result, PSK in addition, which is associated with QAM are used in the majority of data transmission frameworks.

Sidebands extend towards infinity either side: The sidebands of an FM transmission might theoretically go on forever. Even though they are minimal for narrow band FM, they are often important for wideband frequency modulation transmissions. Filters are frequently used to reduce the transmission's bandwidth, but they distort the signal in some way. The majority of the time, this is not a big deal, but it is important to include these filters for wideband FM as well as make sure they are appropriately built.

#### 4.3. MODULATION INDEX AS WELL AS DEVIATION RATIO

It is highly helpful to know how much modulation is actually there in a signal when utilizing a frequency modulated transmission.

This can be used to specify details like the signal's frequency modulation type, for example, whether it is wide-band or narrow-band. It is also highly helpful in making sure that every transmitter as well as receiver in a framework is configured to support a defined amount of modulation for the reason that it influences variables like the receiver bandwidth, channel spacing as well as the like.

Towards defining the level of modulation, figures known as the modulation index as well as deviation ratio are used.

#### 4.3.1. Sinusoidal Baseband Signal

Mathematically, an FM-frequency sinusoidal continuous wave signal can be used to simulate a baseband modulating signal. Single-tone modulation is another name for this technique. An example signal's integral is:

$$\int_0^t Xm(T)dt = \frac{\sin\sin\left(2\pi f_m t\right)}{2\pi f_m}$$

In this case, the expression for y(t) above simplifies to as below:

$$y_{(t)} = A_c 2\pi f_c t + \frac{f_{\Delta}}{f_m} \sin \sin \left(2\pi f_m t\right))$$

In addition, the amplitude Am of the modulating based on the sinusoid remains represented based on the peak deviation  $f_{\Delta} = K_f A_m$ .

A Bessel functions can be used to represent the harmonic distribution of a sine wave carrier modulated via such a sinusoidal signal, which forms the foundation for a mathematical knowledge of frequency modulation in the frequency domain.

#### 4.3.2. Modulation Index

As In other modulation frameworks, the modulation index describes the degree of variation amongst the modulated variable in addition, which is associated with its unmodulated level. Variations in the carrier are relevant frequency.

$$h = \frac{\Delta f}{f_m}$$

Where fm is the highest frequency component found in the modulating signal xm(t), as well as f is the largest variance amongst the instantaneous frequency also carrier frequency. Therefore, the main ratio of the peak frequency based on the deviation of the carrier wave towards the frequency of the modulating sine wave is thought to represent the modulation index for the main of a sine wave modulation. If h << 1, the modulation remains called narrowband FM (NFM), in addition which is associated with its bandwidth is approximately 2Fm Sometimes modulation index h < 0.3 is considered as NFM, otherwise wideband FM (WFM as well as FM).(21)

## 4.4. FM BANDWIDTH

One of An FM signal's bandwidth remains one of its most important components. Any frequency modulated signal has sidebands that extend to either side. These actually go on forever, although their intensity diminishes as they do. Fortunately, it is possible to restrict an FM signal's bandwidth without significantly lowering the situation based on the quality.

Frequency modulation is widely employed in a variety of radio techy applications, including two-way radio communication as well as broadcasting. These applications can make effective use of its unique characteristics.

FM continues to provide the finest quality for broadcasting in addition, which is associated with a number of benefits for other types of communication, even if other forms of modulation are employed in many applications as well.

## 4.5. CARSON'S RULE BASED ON THE FM BANDWIDTH

The calculation of an FM signal's bandwidth is more complicated than it is for an AM signal.

Carson's Rule is a formula often used via engineers to estimate the FM signal's bandwidth for radio broadcasting as well as radio communications frameworks. According to this rule, a bandwidth equal to the deviation frequency plus the modulation frequency contains 98% of the signal power doubled. Carson's Rule can be expressed simply as a formula

BT=

$$2(\Delta f+fm)$$

Where:

$\Delta f$  = deviation BT = total bandwidth (for 98% power) fm = modulating frequency

To Consider a typical broadcast FM signal with a deviation of around 75 kHz which is associated with a maximum modulation frequency of 15 kHz; the bandwidth of ninety-eight percent of the power is roughly 2(75 + 15) = 180 kHz. 200 kHz is allowed for each station in order to provide conveniently spaced channels.

The formula is also highly helpful for figuring out the bandwidth of many two way radio communications frameworks. These utilizations of narrow band FM, in addition, which is associated with it is a significant that the sidebands do not cause interference towards adjacent channels that may be occupied via other users(24).

### 4.6. FREQUENCY MODULATION EQUATIONS

Frequency The baseband signal's integral, which can be either a sine or a cosine, is typically represented via a sinusoidal expression in modulation equations function.

It can be represented mathematically as;

$$m(t) = Am \cos (\omega mt + \theta) \dots \dots \dots \dots \dots 1$$

$m(t) \rightarrow modulating signal$

Where;

$Am \rightarrow$  Amplitude of the modulating signal.  $\omega m \rightarrow$  Angular frequency based on the modulating signal.  $\theta \rightarrow$  is the phase based on the modulating signal.

For instance, amplitude modulation, when we try towards modulating an input signal (information), we need a carrier wave, we will experience

$$C(t) = Ac \cos(\omega ct + \theta) \dots \dots 2$$

Angular modulation, which associated with the main mean  $\omega c$  (*or*)  $\theta$  of the carrier wave starts varying linearly with respect towards the modulating signal like amplitude modulation.

### **4.7. FM DEMODULATOR**

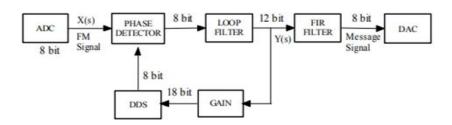

the mid-1970s witnessed the development of computerized stage locked circle as a demodulator which is related to the exhibition as a close ideal FM beneficiary. Figure 2 displays the essential components that go into creating the full FM receiver. The FM receiver is made up of four critical parts: a phase detector, a loop filter, a direct digital synthesizer, as well as (D) FIR Filter.

Figure 4.2. Block Diagram of Digital FM Receiver Circuit.

## 4.8. NOISE REDUCTION

Compared to other techniques, for instance, AM, FM offers a greater signal-to-noise ratio (SNR). Therefore, SNR is much superior to AM. The gains for typical voice communication channels range from 5 to 15 dB. Broader divergence FM broadcasting can result in significantly better outcomes. Additional techniques are frequently used in FM circuits to boost overall SNR, for instance, pre-emphasizing higher audio frequencies deemphasized in the receiver to match. Due to the fixed volume of FM signals, which further increases their acoustic sensitivity, FM receivers commonly have limiters that remove AM noise SNR [25] [26].

## 4.9. QUAD RATURE FM DEMODULATOR

Due to its simplicity of integration into integrated circuits, the FM quadrature demodulator as well as its related coincidence detector or demodulator offer another type of FM detector circuit that is employed in many applications.

The quadrature detector just needs one coil in addition, which is associated with a very small number of other parts. The cost impact can be accommodated for in many radios receiver designs, though, as the inductor is merely a coil which is associated with not a transformer.

The coincidence detector in addition, which is associated with the issue relative, the quadrature detector, both offer high levels of performance with great linearity. [27].

### 4.10. FM QUAD RATURE DEMODULATOR BASICS

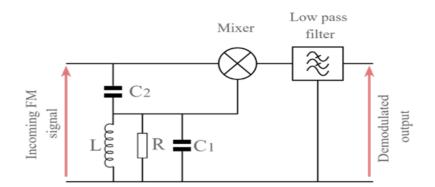

Simple components, for instance, a mixer, a resistor, two capacitors, in addition, which is associated with an inductor make up the quadrature demodulator's circuit. Along with the mixer, there is a low pass filter.

There are two components to the incoming signal. The first signal enters the mixer straightaway, while the second is phase-shifted. The carrier has a 90° phase change, on the other hand, the phase shift will fluctuate slightly as a result of the deviation on the carrier. Based on the magnitude of the deviation.

After that, a multiplier or mixer receives both the original in addition, which is associated with the phase-shifted signals.

Figure 4.3. Demodulator for quadrature FM in.

Phase shift amongst the two signals affects the mixer's output, for instance, It serves as a phase detector in addition, which is associated with generates a voltage output proportional to the phase variance and, consequently, to the degree of signal deviation. The linearity remains excellent if the framework's operation is planned to keep the deviation well away from the  $90^{\circ}$  points.

Performance-wise, the quadrature detector can function at relatively low input levels, It is fairly simple to set up in addition, which is associated with only requires that the phase shift network be tuned to the predicted signal's centre frequency. The frameworks operates down to levels of about 100 microvolts. Additionally, it has strong linearity, which leads to little distortion (27).

# 4.11. QUADRATURE DETECTOR ADVANTAGES & DISADVANTAGES

# a) Advantages of FM quadrature demodulator

- Offers good level of performance in addition, which is associated with including linearity.

- Can be incorporated into an integrated circuit.

- Very simple circuit easy towards ensuring it operates correctly.

# b) Disadvantages of FM quadrature demodulator

- Requires the utilization of a coil this not a major issue as a simple coil is utilized in addition, which is associated with an RF transformer is not needed as in the case of the ratio as well as Foster Seeley circuits.

- Some designs may require setting during manufacture.

## **CHAPTER 5**

## VHDL -HARDWTHAT ARE DESCRIPTION OF THE USED LANGUAGE

VHDL remains a term it alludes to the Hardware Description Language (HDL) for Very High Speed Integrated Circuits (VHSIC) (VHSIC). A computer language called VHDL is utilized to describe a logic circuit via describing how its structure as well as data flow behave.

The Field Programmable Gate Array (FPGA) of a Programmable Logic Device (PLD), which includes one, is configured utilizing this hardware's description utilizing a conventional logic design. A formal language called VHDL is also utilized to specify the structure in addition, which is associated with the behaviour based on the main digital circuit.

# 5.1. VHDL BASED ON SEVERAL CONCEPTS

The goal of VHDL remains utilized towards describing a main model of a piece of digital hardware that shows both the device's exterior in addition, which is associated with the one as well as more of its interior views. Despite the fact the internal based on the view of the device shows its structure as well as its interface, which allows it to connect with several models based on the same environment, the external view shows the device's physical appearance based on the main functionality.

#### 5.1.1. Behavioural based on Modelling

The most basic formula based on the behavioural modelling of VHDL remains the signal assessment statement as presented in the instance below:

The previous the value of b is transferred to an in the example. Signal an is replaced via signal b as a result of this statement. This statement is carried out whenever the signal b's value is modified. This statement's sensitivity list is signal b. When a signal in a signal assignment statement's sensitivity list changes value, the signal statement is executed. The target signal based on if the main associated execution resulted in a new value that differs from the signal's current value. Since no event will be scheduled if the execution outcome value is the same, the transaction will still be generated. Only changes in value are utilized towards scheduling events, whereas transactions are always created when a model is evaluated.

Even though the main transaction which remains always created as soon as the main model remains evaluated, only changes in signal value for events towards being scheduled.

#### 5.1.2. The Main Structural Modelling

The structural it is a simulation of the frameworks since description specifies the logical components of the frameworks. The components could be AND or OR gates, or they could be at the main higher of logical level, such processor level or register transfer level (RTL). For the frameworks that needs explicit design, the main structural description remains more frequently employed than the behavioural description. In the same way, if the researchers wish to use (A+B=C), we must. In behavioural design, sometimes the researchers must utilize the formula (C = A + B), in addition, which is associated with the we are unable to choose the sort of adders that will be utilized. This addition process.

The structural description in addition, which is associated with the whole statements are contemporaneous. All of the statements that include an event happening simultaneously across any simulation time.

The main availability based on several elements (especially primitive gates) for the user is the primary distinction amongst the structural descriptions in VHDL as well as Verilog. Verilog recognizes all primitive gates, including AND, OR, XOR, NOT, in

addition, which is associated with the XNOR. For the gates to be recognized via libraries, packages, or modules that provide descriptions of gates, the VHDL packages.

#### 5.1.3. RTL based on the Register Transfer Level based on several Diagrams

Register-transfer level (RTL) that was utilized in the design of digital circuits models the asynchronous digital circuit in terms of the flow of digital signals amongst hardware registers in addition, which is associated with the the logical operations on those signals. In hardware description languages (HDLs) like Verilog in addition, which is associated with VHDL, register-transfer level abstraction is utilized to create high-level representations of circuits from which lower-level representations as well as ultimately actual wiring remain formed. RTL design is viewed as a unique technique for contemporary digital design [28].

In contrast with software if register-transfer level intermediate exemplification is the lowest level in compiler design, RTL level is the typical input that circuit designers work on. There are other levels above it. Actually, a transitional language amongst the input register transfer level representation in addition, which is associated with the destination netlist is utilized during the synthesis of the circuit. In contrast to netlist, structures like cells, functions, in addition, which is associated with the multi-bit registers are existed [28].

### 5.2. VHDL DESIGN STAGES

## 5.2.1. Entity

Entire designs are formulated utilizing entities. The entity is the most fundamental design building block. The VHDL entity determines the entity name, entity ports, in addition, which is associated with the interest group information. The use of one or more entities results in the creation of entire designs [29]. When a hierarchical design is utilized, the main description of the main associated top-level which will also include a description of the lower-level contained in it.

### 5.2.2. Architecture

The architecture in all entities that may be emulated, a description is present. The architecture gives an account of the entity's behaviour. Each entity contains elements from diverse architectures. Various architectures can be behavioural descriptions of the same thing, while others can be structural descriptions. design.

## 5.2.3. The Main Package

The primary objective of the package is to compile the components that can be shared (globally) via two or more design units. A package is a common form of storage that can be utilized towards house INFO that will be shared among many diverse entities. Data can be shared through packages, as well as the declaration of the data inside the package makes it possible for other packages to reference the data entities.

Each A package body in addition, which is associated with the package declaration section are its two constituent sections. In the same way, that the entity defines the model interface, the main associated package interface is defined via the package declaration. The package body, in a manner similar to how the architecture statement handles it, specifies the actual behaviour of the package. Based on the main associated model.

### 5.2.4. Process

The basic Process is the VHDL execution unit. The operations carried out in a simulation of a VHDL can be divided into single in addition, which is associated with the multiple processes. Which required as a description.

## **5.3. VHDL MODELLING BASICS**

## 5.3.1. Constants

The constant Objects are labels applied to a certain type value. Constants give you the ability to construct a model that is both properly documented in addition, which is associated with the simple to update. Constants, for instance, are employed when a model requires the same value for a variety of instances. The designer can modify the constant value as well as compile such that the entire set of instances will reflect the new value of the constant.

### 5.3.2. The main associated Signals

Models are formed via the connection of entities together via utilizing signal objects. The communication of dynamic data amongst entities is implemented via signals. A declaration of the signal is written is as follows:

SIGNAL signal\_name: signal\_type [:= initial\_value];

Signal name(s) the word "SIGNAL" is placed after it. Each name of a signal results in a separate signal. The signal type as well as name are divided via a colon. What is meant via "kind of signal" is the kind of information that makes up the main required signal.

A specifier for the signal's initial value may be included, allowing for the initialization of the signal's value. The signal can be declared in the package declarations, architecture declarations, in addition, which is associated with the entity declaration sections. For the reason that they may be shared amongst multiple devices, signals declared in the package are referred towards as global signals. As well as entities.

## 5.3.3. VHDL Operators

There are six categories of predefined operators in the language in addition, which is associated with the main associated of these operators can being described as follows:

- An additional operators

- Multiplication based on operators

- Relational based on the operators

- Logical operators

- Shift operators

- Miscellaneous operators

Each operator beginning with category (1), has increased prominence to (5). The evaluation is carried out from left to right, as well as operators positioned in the same classification have the same precedence. The ability towards override the main left-towards-right based on the evaluation based on utilizing of parentheses.

### **5.3.4.** Concurrent Based on a Signal Assignments

Each assignment as well as statement Implementations are made sequentially in a common computer language, for instance, C as well as C++. The sequence of implementation is based on the source file's statement order. The assignment statements inside the VHDL design are not in a specific order. Only events that signify which the assignment statements should be implemented in which sequence within the VHDL architecture are sensitive to.

### **CHAPTER 6**

### **IMPLEMENTATION OF FM RECEIVER IN FPGA**

The implementation of the FM receiver in FPGA has two stages: Hardware development in addition, which is associated with the software development in VHDL.

## 6.1. HARDWARE DEVELOPMENT

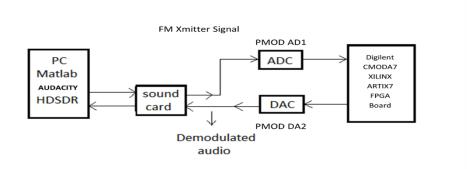

Hardware part of the study incorporates PC, FPGA card, ADCin addition, which is associated with DAC cards. In the same way, the general understanding based on the frameworks is presented in Figure. 6.1. Below

Figure 6.1. The main general representations based on the FPGA (FM) Receiver.

FPGA card Digilent CMODA7-35T, which has a Xilinx Artix7 FPGA embedded on it, is the component in the framework [30]. The 20K-LUT, 225KB Block-RAM FPGA chip's model number is XC7A35T, in addition, which is associated with the it comes in a 1CPG236C package. The board includes 512KB of SRAM with an 8-bit bus in addition, which is associated with an 8-ns access time, 4MB of Quad-SPI Flash to store FPGA programs, as well as a USB-JTAG programming facility that also draws power from the linked USB bus. There are a total of 48 pins on each side of the DIP-shaped board. A solderless breadboard serves as the means of all board connections. 44

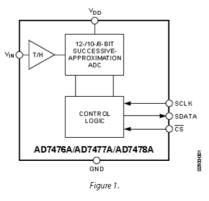

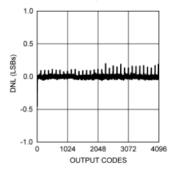

Digital GPIO pins with 3V3 logic capability are available on the board. A dual channel 1MSPs/channel 12-bit A/D converter chip, the AD7476, is incorporated into the Digilent PMOD-AD1 ADC board [31]. A standardized PMOD connector serves as the card's interface. The Digilent PMOD-DA2 DAC card features two DAC121S101 1MSPs 12-bit DAC chips [32]. Once more, a PMOD connector serves as the interface.

The FMRX frameworks may also receive test signals from in addition, which is associated with the external USB sound cards, while the PC's internal sound card is just utilized for results monitoring as well as listening.

As shown in figure 6.1, the soundcard speaker output plays back the recorded test signal (a modulated FM wave) at 48KSps. This signal is converted to digital form via the A/D card before being processed via the FPGA board. After the signal has been processed in addition, which is associated with the demodulated via the FPGA's internal architecture, which is built via programming with VHDL code, the software development section provides more information about this process. After that, a D/A card receives the digital output as well as converts it to analog at a 48KSps rate. It is then taken through the soundcard's microphone input as well as transferred to the PC for monitoring, recording, as well as listening purposes. The HDSDR SDR software environment on the PC is utilized to continue monitoring the demodulated stream. Figure displays a picture of the frameworks in Figure 6.2.below.

Figure 6.2. Photo of the frameworks in Operation

# 6.1.1. FPGA Board Spartan CX7A35T

# 6.1.1.1. Introduction

The Spartan-FPGA from Xilinx is a user-friendly FPGA board that was created to help people learn about in addition, which is associated with the experiment with designing frameworks utilizing FPGAs.

This newly created board features a 512KB SRAM chip from Xilinx in a 1CPG236C package with an 8-bit bus in addition, which is associated with the 8ns access times. 4MB Quad-SPI Flash.

Figure 6.3. FPGA developed BOARD SPARTAN CMODA7-35T

Includes a USB-JTAG programming The Spartan-FPGA from Xilinx is a user-friendly FPGA board that was created to help people learn about as well as experiment with designing frameworks utilizing FPGAs.

This newly created board features a 512KB SRAM chip from Xilinx in a 1CPG236C package with an 8-bit bus in addition, which is associated with the 8ns access times. 4MB Quad-SPI alike.

## 6.1.1.2. Board Based on Some Features

FPGA: Spartan XC7A35T in 1CPG236C based on the package

• 512KB SRAM with an 8-bit bus and 8ns access times

- 4MB Quad-SPI Flash

- USB-JTAG Programming Circuitry

- Powered from USB or external 3.3-5.5V supply connected to DIP pins .

# 6.1.2. Analog to Digital Signal Converter

# 6.1.2.1. Introduction

The Digilent PmodAD1 is a 12-bit, two-channel analog-to-digital converter that uses the Analog Devices AD7476A. This Pmod can perform well in even the most demanding applications thanks to its sampling rate of up to 1 million samples per second audio applications.

Figure 6.4. The Analog to Digital Signal Converter.

# 6.1.2.2. Board Features

- Two channel 12-bit analog-to-digital converter

- Simultaneous A/D conversion at up towards one MSa per channel

- Two 2-pole Sallen-Key anti-alias filters

- Small PCB size for flexible designs 0.95 in × 0.8 in (2.4 cm × 2.0 cm)

- 6-pin Pmod port with GPIO interface

- Library in addition, which is associated with the example code available in resource center

## 6.1.3. Digital to Analogy Signal Converter

## 6.1.3.1. Introduction

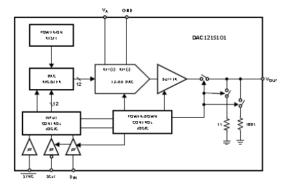

The Digilent Pmod DA2 is a 2 channel 12-bit Digital-to-Analog Converter module capable of outputting data up to 16.5 MSa .

Figure 6.5. Digital to Analogy Signal Converter.

#### 6.1.3.2. Board Features

- 12-bit digital-to-analog converter

- Two simultaneous conversion channels

- Very low power consumption

- 6-pin Pmod connector with GPIO interface

# 6.2. PROGRAMS

Based on this research study, the third party based on the software packages remain utilized in the main associated various stages. These programs in addition, which is associated with the their role in the study remain given in the next sections in detail.

# 6.2.1. Matlab

The significance Realistic SDR implementation requires certain tools, for instance, a fast A/D converter in addition, which is associated with the potent signal processor,

which is why we utilized MATLAB in our work. For students studying radio communication, this equipment drives up the cost of the hardware platform. For the reason that of this, the radio signal frequency in the audio band is constrained, therefore Matlab was utilized in our investigation. The receiver configuration was covered in one Matlab session. Each modulation as well as demodulation study is completed utilizing Matlab as well. The only options the user must choose from while utilizing this frameworks are modulation in addition, which is associated with the demodulation as well as the main corresponding of some factors.

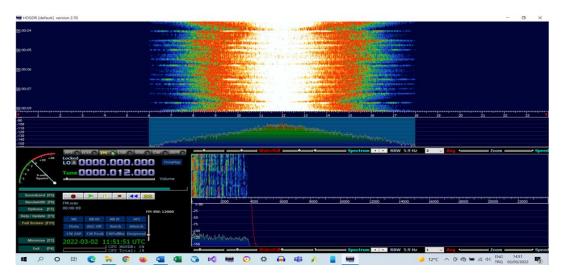

## 6.2.2. HDSDR

HDSDR is SDR a program that listens to radio broadcasts, analyzes the spectrum, as well as evaluates the outcomes. The input in addition, which is associated with the output signals are separated from one another via a waterfall in addition, which is associated with a wide range. The lower speed waterfall spectrum is achieved without noise, in addition, which is associated with the the signals created via similar Matlab scripts are received as well as transmitted. The waveform that the PC's sound card produces is monitored as well as recorded via HDSDR. Additionally, it functions with a recording scheduler to record in addition, which is associated with the replay RF, IF, as well as AF WAV files. In order to properly sync the pitch amongst sources, the main (HDSDR) as a software enables a user to enter the mode in addition, which is associated with the global offsets the radio as well as the main required (SDR) based on the audio.

### 6.2.3. The Audacity

It is utilized is a program for both recording in addition, which is associated with the listening. A strong audio editing as well as recording package may be utilized with it with ease. It enables the recording of voices, the editing of recorded voices to fix any pronunciation errors, in addition, which is associated with the blending of several sound recordings from various sources, for instance, music, interviews, or other sound recordings. Since Audacity permits exporting of recordings in MP3 format, it is appropriate for creating podcasts.

#### **6.3. SIMULATION STUDIES**

Simulation The frequency modulated waveform is produced utilizing the transmitter code listed on Appendix A.1, while simulation of the reception is carried out utilizing the receiver code listed on Appendix A.2. The code listing on Appendix A.3 provides a means for examination of the frequency modulated waveform the results.

The test of the An FM waveform created utilizing transmitter code is utilized via FPGA FM receivers (fmrx). The modulating signal utilized via the code is a 10s sample music recording sampled at 8KSps in wav format, resulting in a bandwidth of only 4KHz. To handle the final modulated signal, which is normalized as well as then stored in a wav file called FM.wav at the conclusion of the code, it is up sampled to 48KSps. The baseband signal was submitted for integration after it had been normalized to the +1 range. Prior to integration, it is rescaled utilizing a modulation coefficient that establishes the real maximum frequency which in turn determines the modulating signal bandwidth which remains (4KHz) as said before. Maximum frequency deviation Fdmax is derived utilizing the formula below:

$$F_{dmax} = \frac{A_{max}}{2.\pi.T_s}$$

Here,

F<sub>dmax</sub>: Maximum frequency deviation (Hz), A<sub>max</sub>: Maximum amplitude (rad),

Ts: Sampling period (s)

With the Amax given in the code  $F_{dmax}$  is 2KHz. After integration of the signal, it is added to the carrier signal phase argument, whose center frequency is set to 12 KHz. Thus, phase modulation a common technique for creating FM in sampled frameworks remains employed to create an indirectly frequency modulated output. A bandpass filter with a central frequency of 12 KHz in addition, which is associated with the bandwidth of + 6 KHz is utilized to filter the modulated carrier. For the reason that of what Carson's rule tells us, the bandwidth has been chosen at 12 KHz equation suggests:

$$BW_{FM} = 2.(F_{dmax} + BW_m) = 2.(2KHz + 4KHz) = 12KHz$$

Thus, modulation index  $\beta$ , of the frequency modulated carrier is:

$$\beta = \frac{F_{dmax}}{BW_m} = \frac{2KHz}{4KHz} = 0.5$$